В этой части я решил добавить немного управления в радиоприёмник, а точнее выбор частоты и моды (LSB/USB).

А также заложить все базовые элементы управления, которые очень пригодятся в дальнейшем.

Т.к. мощности используемого FPGA модуля очень ограничены, он является очень бюджетным, то было решено вынести органы управления под управление платы Arduino UNO.

Тем самым сэкономив дорогие логические блоки FPGA, отказавшись от прямого опроса энкодера, вывода на дисплей информации и первой логики управления приёмником, которая дальше будет только расти.

В роли дисплея выступает LCD модуль от Nokia 5110, в роли энкодера модуль KY-040.

Общение между процессором ардуино и FPGA было решено организовать по протоколу UART.

Также, требованием этой части работ было перманентное сохранение конфигурации FPGA во флеш-память, ранее требовалась перепрошивка каждый раз после включения устройства.

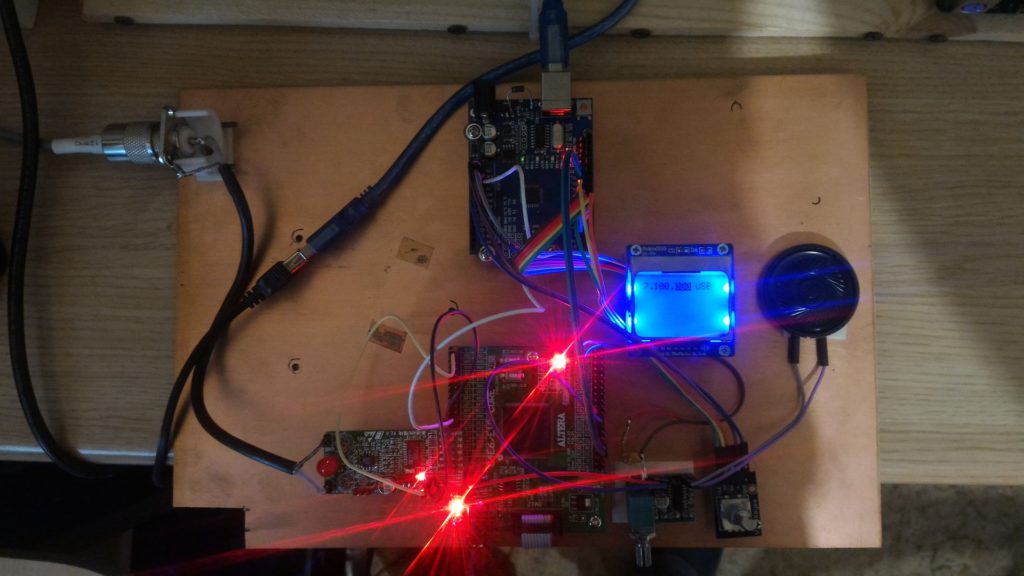

После сборки всех элементов получилась следующая цветомузыка конфигурация:

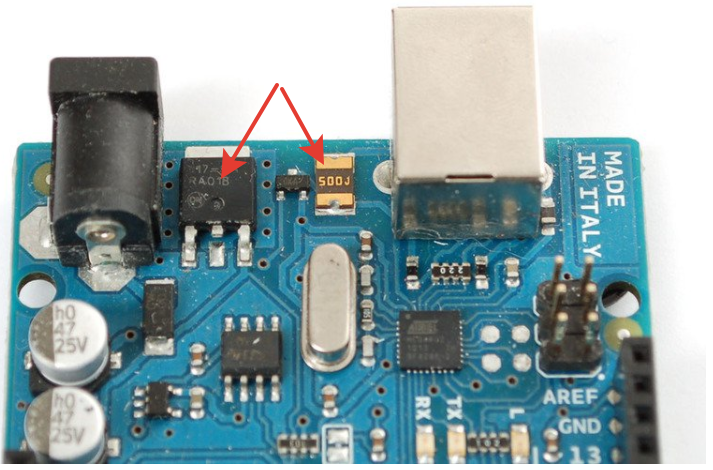

Подключать Arduino UNO сразу к FPGA нельзя, т.к. ардуино использует высокие логические уровни (5 вольт), а ПЛИС до 3.3в (стандарт — 2.5в).

Для этого меняем стабилизатор напряжения на аналогичный, с 3.3в на выходе. Вместо предохранителя питания ставим диод.

Подробнее процесс описан в статье https://learn.adafruit.com/arduino-tips-tricks-and-techniques/3-3v-conversion

Итак, первым делом станет подключение процессора внутри ПЛИС. То есть на логических элементах матрицы FPGA генерируется процессор, эдакая микросхема в микросхеме.

Это просто поразительно — можно совместить огромнейшие вычислительные мощности FPGA и при этом управлять ими с помощью обычного процессора и прошивки на языке C. Например, на одной микросхеме можно собрать видеоадаптер HDMI, эмулировать процессор ZX Spectrum, перефирию и память (и впасть в ностальгию).

Данный эмулируемый процессор называется NIOS II.

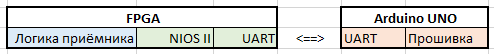

Блок схема работы управления будет выглядеть так:

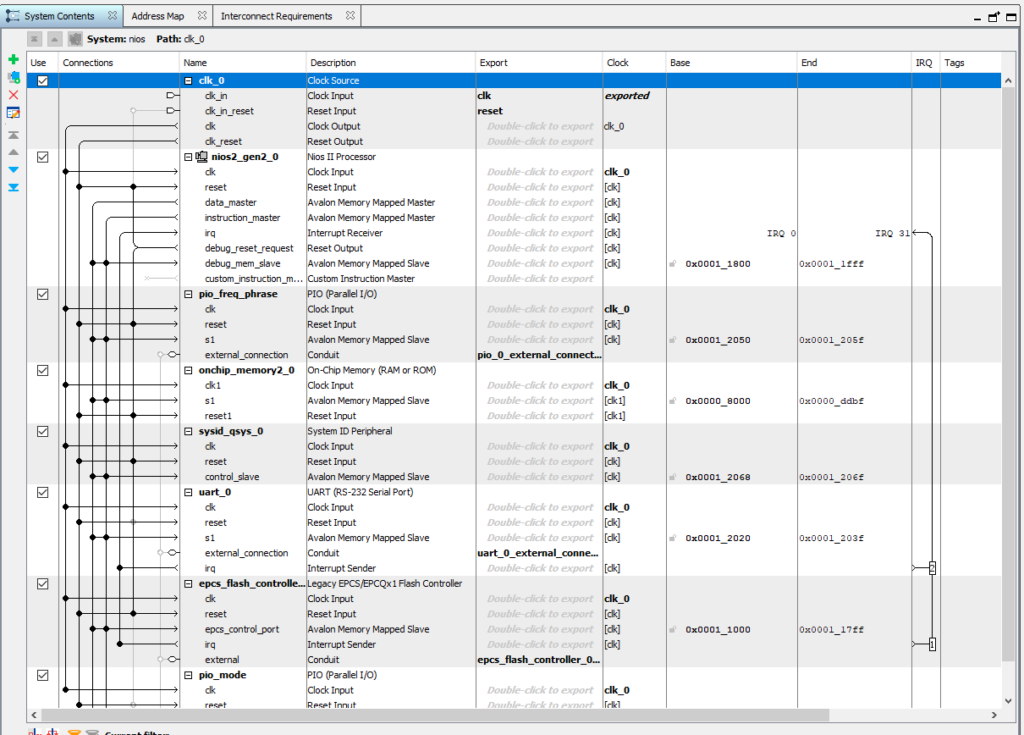

При создании процессора в Quartus программа предлагает добавить к процессору периферию, выбираем:

- clk — тактовый генератор процессора

- nios2 — собственно сам процессор

- pio_freq — GPIO выводы управления частотой гетеродина

- onchip_memory — ОЗУ, в моём случае 24 килобайта, пока этого достаточно

- sysid — система идентификации прошивки процессора

- uart — модуль общения с внешним миром, настроен на скорость в 57600 бод

- epcs_flash — модуль запили прошивки во внешнюю флеш-память

- pio_mode — GPIO вывод управления модой (LSB/USB)

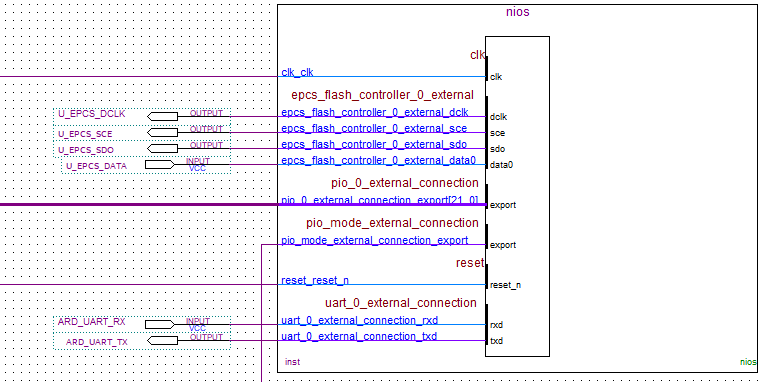

Теперь мы можем добавить процессор на логическую схему.

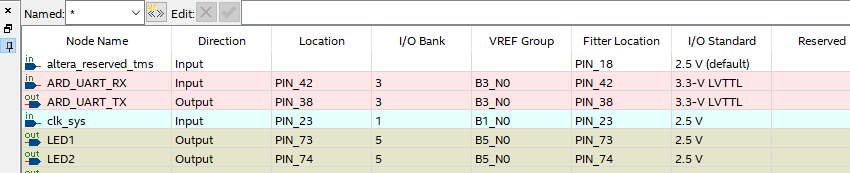

соединяем выводы clk с кварцевым генератором, пины epcs на выводы, идущие к флеш-памяти. PIO на соответствующие модули гетеродина и демодулятора. UART входы и выходы не забываем переключить в режим 3.3v в Pin Planner.

Открываем среду разработки процессора Nios 2 (Tools->Nios II Software Build Tools for Eclipse) и создаём новый проект.

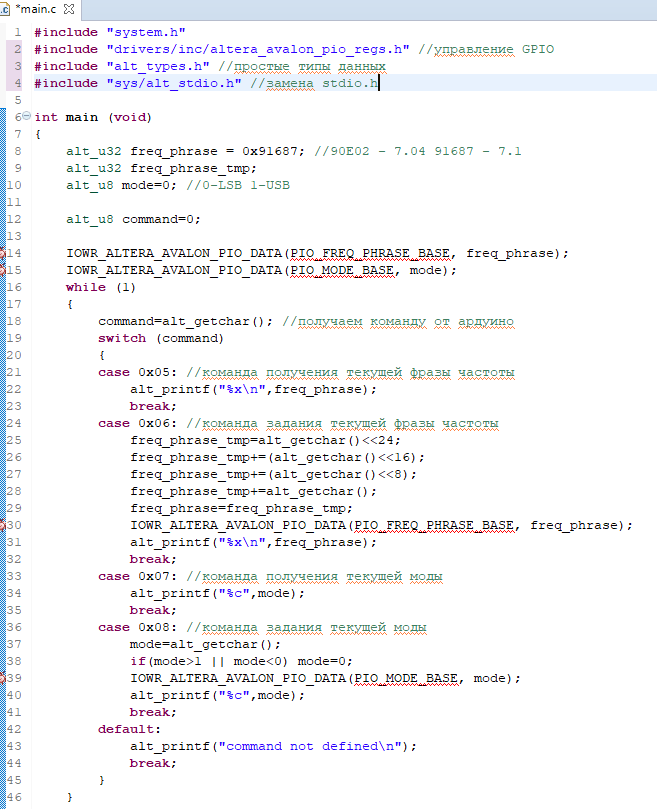

Программный код очень прост — читаем данные из UART, в зависимости от первого байта (команда) меняем или отсылаем необходимые данные.

Главной особенностью стоит назвать использование библиотеки alt_stdio.h вместо stdio.h, которая тянет за собой огромную кучу зависимостей, мгновенно съедая всю доступную память процессора (и даже больше).

После первой прошивки получившейся сборки у нас открывается возможность программировать память FPGA и его Nios во флеш память. Для этого был написан небольшой bat-файл, автоматизирующий все действия.

SET PATH=%PATH%;C:\intelFPGA\17.1\nios2eds\bin;C:\intelFPGA\17.1\quartus\bin64;C:\intelFPGA\17.1\nios2eds\bin\gnu\H-x86_64-mingw32\bin

sof2flash —input=»output_files\UA3REO.sof» —output=»output_files\hwimage.flash» —epcs —verbose —debug

elf2flash —input=»software\ua3reo_nios\ua3reo_nios.elf» —output=»output_files\swimage.flash» —epcs —after=»output_files\hwimage.flash» —verbose —debug

nios2-flash-programmer «output_files\hwimage.flash» —base=0x11000 —epcs —accept-bad-sysid —device=1 —instance=0 —cable=1 —program —verbose

nios2-flash-programmer «output_files\swimage.flash» —base=0x11000 —epcs —accept-bad-sysid —device=1 —instance=0 —cable=1 —program —verbose —go

pause

Суть команд в следующем:

sof2flash подготавливает SOF прошивку FPGA для прошивки во флеш память;

elf2flash делает аналогичные действия для прошивки Nios 2;

nios2-flash-programmer их поочереди прошивает.

Теперь приёмнику не страшна перезагрузка или отключение питания, всё заработает мгновенно после включения.

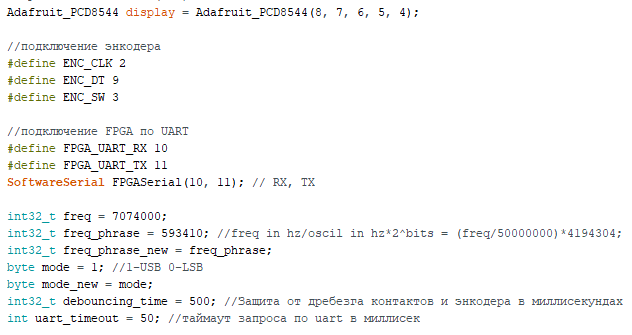

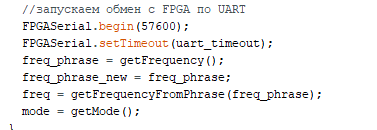

Финальным этапом будет разработка приложения для ардуино. Кратко пробежимся по коду.

Задаём настройки выходов, инициализируем переменные.

Важно отметить что ключевые переменные вроде частоты и моды продублированы — это необходимо чтобы разделить выполнение кода прерываний (энкодера) от основного цикла.

Это сделано в силу того, что мы не можем по прерыванию сразу отправлять данные в UART. Во первых, во время работы прерывания не доступны функции delay, millis и прочие, связанные со временем. Во вторых передача данных может занять некоторое время, и «плавность» работы энкодера будет нарушена.

Запрашиваем текущие параметры с приёмника

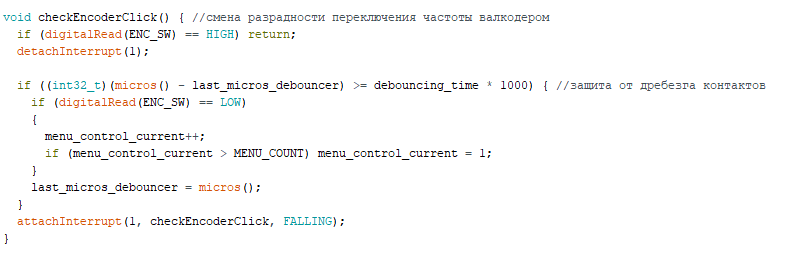

Избавление от дребезга контактов при нажатии энкодера реализовано через отключение прерывания внутри прерывания)))

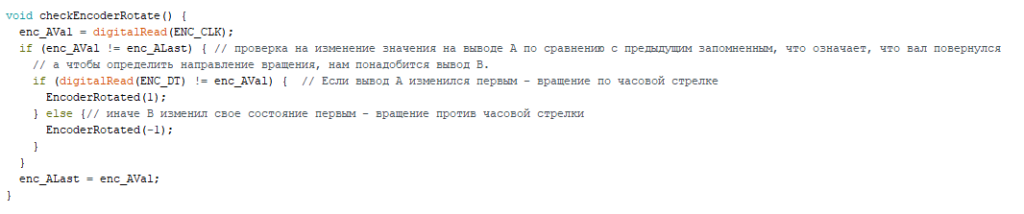

Прерывание для обработки вращения энкодера

Остальной код можно увидеть в исходниках, доступных по ссылке ниже.

Видео работы проекта, прошу заметить что приёмник не обладает УВЧ совсем, и 5-ти вольтовый АЦП пытается выудить из микровольтного сигнала хоть что-то. УВЧ думаю доделать в ближайших частях, когда придут запчасти.

Код проекта доступен по ссылке.

Статьи, используемые при разработке этой части:

- http://we.easyelectronics.ru/plis/altera-nios-ii-qiuckstart-osvaivaem-principy-postroeniya-sistemy-i-infrastrukturu-sborki.html

- https://learn.adafruit.com/arduino-tips-tricks-and-techniques/3-3v-conversion

- https://github.com/adafruit/Adafruit-PCD8544-Nokia-5110-LCD-library/blob/master/examples/pcdtest/pcdtest.ino

- https://marsohod.org/index.php?option=com_content&view=article&id=261:sfl&catid=11:blog&Itemid=26

- http://www.naliwator.narod.ru/les_nios.html

- http://acvarif.info/artplis/artplis3.html

- http://arduino.ru/

Добрый день!

Вы уже развели nios в fpga — для чего ардуино?

Количество используемых логических элементов не зависит от размера программы для nios — она во флеше хранится.

Добрый день!

Это промежуточный этап реализации — дальше вместо ардуины появляется STM32, в котором будет большая часть обработки. Потом кстати и от NIOS отказ идёт.