Очередное обновление проекта.

+HARDW: Отказ от второго ОУ в драйвере, с RD07MVS1 он не нужен

Применение мощный транзисторов в оконечном каскаде позволило отказаться от второго каскада предусилителя, с ним возникает перегруз.

+FPGA: Обзор FFT расширен до 96кГц, улучшена работа моды WFM (широкополосное радиовещание)

По заявкам желающих)) Панорама расширена до 96кГц, но по прежнему имеет возможность приближения вплоть до х16 через настройки. Широкая полоса используется при приёме WFM модуляции радиовещательных станций. Обновите параметр CIC Shift (в меню калибровки) на 83, если обновляетесь с прошлых версий.

+STM32: ШИМ для управления оборотами вентилятора

Автоматическая подстройка скорости вращения вентилятора при длительной работе на передачу.

+STM32: Новый стиль S-метра // Thx to UR5NKA

Стиль отображения «стрелкой», пример можно увидеть на видео в конце статьи.

+STM32: Удален неиспользуемый код управления яркостью

Т.к. сейчас спящий режим не используется в проекте.

+STM32: Управление усилением AGC вынесено в настройки

Целевое усиление добавлено в настройки, теперь можно подогнать громкость под любые колонки или гарнитуру.

+STM32: Новый способ переключения мод (группа->мода): LSB->USB, CW_L->CW_U, DIGI_U->DIGI_L, NFM->WFM, AM->IQ->LOOP

Упрощает жизнь, т.к. мод много, и поиск нужной занимает много времени, теперь они сгруппированы по типу.

+STM32: Периодическая синхронизация времени через SNTP

Время синхронизируется с заданным интервалом, а не только при включении трансивера.

+STM32: WiFi CAT интерфейс

Виртуальный CAT интерфейс позволяет не подключая трансивер к компьютеру удобно вести аппаратный журнал, заполняя моду и частоту. (и не только, весь функционал CAT Доступен по беспроводной сети).

+STM32: Доработки компрессора микрофона + регулировка усиления из меню

Доработки качества звучания в режиме SSB

+STM32: Автоматический выбор источника сигнала при передаче

Если забыть выбрать в меню истоник сигнала (MIC/LINE/USB), то при определенных ситуациях он выбирается автоматом.

+STM32: Исправление ошибок

Много разных и мешающих жить)

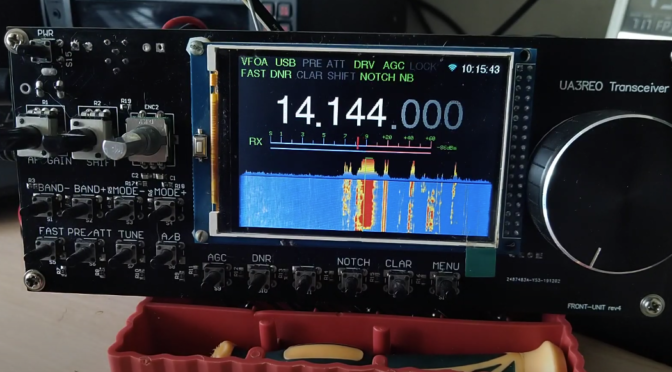

Видео работы прошивки 1.9.3 на приём и передачу:

Архив проекта версии 1.9.3

Репозиторий проекта на GitHub

Архив статей по проекту

Дмитрий благодарю вас за видео и обновление проекта . Всё смотрится классно .

Дмитрий добрый день. А Вы не прибывали кнопки делать на резистивных делителях? По идее на один канал АЦП можно половину кнопок вывести.

Гениально! Спасибо за идею! попробую…

Это был не подкол, а обычный вопрос. Если был печальный опыт, хотелось бы услышать, что не получилось. Ни в коем разе не хотел Вас обидеть.

Да я и не смеюсь, идея и правда отличная, включил в план на реализацию. Я ранее не пробовал, но думаю будет отлично работать, по 3-4 кнопки на вход повесить и будет отличная экономия. И даже отрабатывать быстрее будет.

Прототип новых плат я уже заказал, жду, но к последующей ревизии обязательно попробую.

Думаю при 3,3в АЦП можно и 5-7 кнопок запустить, как тут например: http://www.cqham.ru/forum/showthread.php?34517-Synthesizer-on-Mega-2560-3-2-TFT-LCD-Si5351-V2-0

Подробные фото всей конструкции сделайте, пожалуйста.

Хорошо, выложу вместе со следующей версии прошивки, чтобы было в одной статье.

Кнопки с резистивными делителями icom вовсю применяет. Подтяжка 6.8 к и в цепочке 2.2, 4.7 и 13 килоом. Слямзил к себе — работает даже с 5% резисторами.

Редкий широкополосный трансивер, интересно. Возможно, вам удастся использовать msi001 для изготовления дешевого портативного приемника.

Дмитрий, Вы не замечали сильно ли плывет частота на используемом Вами генераторе? Нашел более стабильный, но не понимаю можно ли его заменить: https://www.aliexpress.com/item/4000010076040.html?spm=a2g0o.cart.0.0.27973c00disN6X&mp=1

Эх, если бы я раньше его заметил — применил бы… жаль…

Да, частота плывёт, потому что применён VCXO, а не TCXO генератор. В версии трансивера 2.0 будет синхронизация VCXO генератора силами низкочастотного TCXO на 10мгц (либо сигнала с GPS), платы уже приехали и почти собраны.

Но вы можете использовать и этот TCXO генератор, должен работать отлично.

Подскажите, при его использовнии обвязка и подтяжка соответсвенно не нужны или? И как быть со вторым отрицательным выходом на ПЛИС?

Вот такие еще есть генераторы, он же используется в разработке Генадия «Аист-2»: https://www.aliexpress.com/item/4001038532041.html?spm=a2g0o.cart.0.0.53ca3c00irBSch&mp=1

судя по данным у него стабильность тоже не очень +-20ppm

Первым делом на тестовом стенде проверьте какие у него уровни — скорее всего будет TTL 3.3v. Если всё так — убираете подтяжки уровней LVPECL, в прошивке FPGA меняете тип входа с дифференциального LVPECL на одиночный TTL, ну и всё.

АЦП/ЦАП вполне корректно заработают и без отрицательного вывода.

Здравствуйте, подскажите пожалуйста, когда вы будете продавать платы на трансивер? Будет ли проект коммерческим? Спасибо заранее.

Добрый день! с выпуском версии 2.0 (пока с мелким экраном) буду распродавать оставшиеся от заказа платы, они у меня уже на руках, но пока не собраны и не проверены.

А в целом коммерческие цели не преследую.