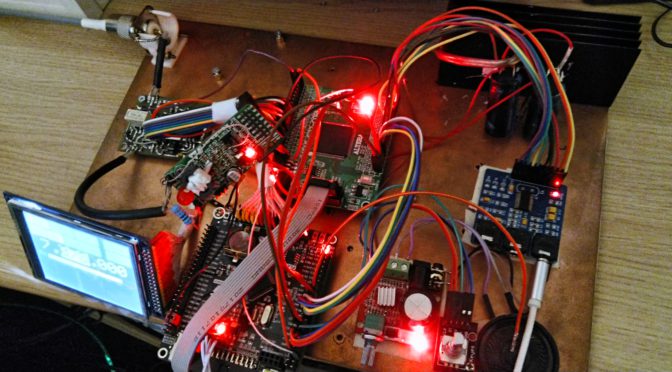

Статья является продолжением цикла записей о создании цифрового DDC приёмника. Теперь поговорим о передающем тракте и сборке проекта во что-то более-менее автономное и законченное.

Первым делом был реализован ЦАП на DAC904E, конструкция пока не закончена — необходимо поменять трансформатор на ADT1-1WT, отладить и закрыть в экран. Схема и плата доступны тут.

Также, был реализован весь код передачи в FPGA, по сути это тот же процесс приёма, только перевёрнутый назад. Переключение происходит через блоки MUX по команде CPU.

Но тут же и ждало разочарование, на первую передачу ушло все 22к логических блоков, доступных мне FPGA. Фильтры получились с достаточно посредственной АЧХ, а о расширении функционала не могло быть и речи.

Поэтому было решено в очередной раз заменить управляющую плату, в этот раз с Arduino DUE на Cortex-M4 STM32 STM32F407VET6 (купил в китае тут).

Для работы с ним я использовал IDE Keil и STM32CubeMX (необходимо установить как минимум, чтобы посмотреть распиновку подключения между платами и собрать проект).

Суть модификации заключается в следующем:

- Это более мощный процессор, соответственно отзывчивость интерфейса на максимуме.

- Аппаратная работа с DSP, что позволяет вынести низкочастотную часть по фильтрации, преобразованиям Гилберта и прочим в CPU, освободив место в FPGA.

- Поддержка шины FSMC, что позволяет подключить 16ти битный параллельный LCD экран ILI9341, где можно очень быстро выводить всю нужную информацию, в том числе и FFT анализатор с водопадом.

На текущий момент реализовано взаимодействие между CPU и FPGA, и в STM32 поступает IQ аудио-поток дискретизацией в 48кГц, который используется для построения FFT и водопада. Но само преобразование и вывод аудио-сигнала пока лежит на плечах FPGA, это будет следующий этап разработки. Но уже сейчас работает передача, вывод TUNE сигнала, АРУ и прочие основные фишки полноценного трансивера.

Ссылка на файлы проекта.

Полезные статьи, используемые в проекте:

- http://k6jca.blogspot.com/2017/02/an-fpga-sdr-hf-transceiver-part-1.html

- http://k6jca.blogspot.com/2017/03/an-fpga-sdr-hf-transceiver-part-2-fpga.html

- http://www.ti.com/lit/ds/symlink/dac904.pdf

- https://www.cs.indiana.edu/~geobrown/book.pdf

- https://arachnoid.com/PLSDR/

- https://www.st.com/en/microcontrollers/stm32f407ve.html

- http://wiki.stm32duino.com/images/2/26/STM32F407VET6_pinoutDiagram.pdf

- http://wiki.stm32duino.com/images/5/5c/STM32_F4VE_SCHEMATIC.PDF

- https://cdn-shop.adafruit.com/datasheets/ILI9341.pdf

- http://narodstream.ru/stm-urok-37-displej-tft-240×320-8bit-chast-1/

- https://hubstub.ru/display/51-kak-poluchit-koordinaty-tochki-kasaniya-i-proizvesti-kalibrovku-rezistivnoy-sensornoy-paneli-na-primere-xpt2046.html

- http://eugenemcu.nichost.ru/articles/applications/265-stm32-fft

здравствуйте, а можно структурную схему соединений всех модулей?

Добрый день! в данный момент схема поддерживается в файле UA3REO.dch (https://github.com/XGudron/UA3REO-DDC-Transceiver/tree/master/Scheme), для просмотра и редактирования потребуется программа DipTrace