Небольшие доработки входного тракта и разрядости выходного.

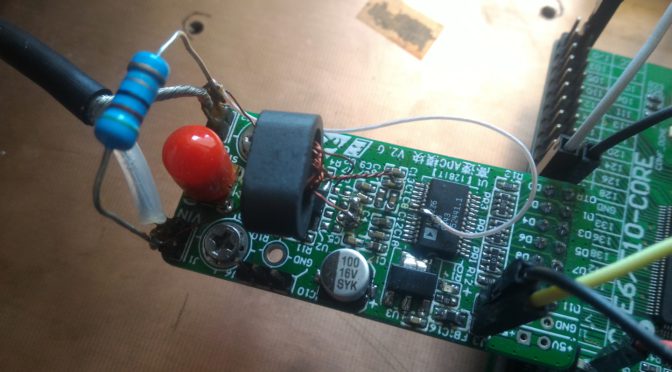

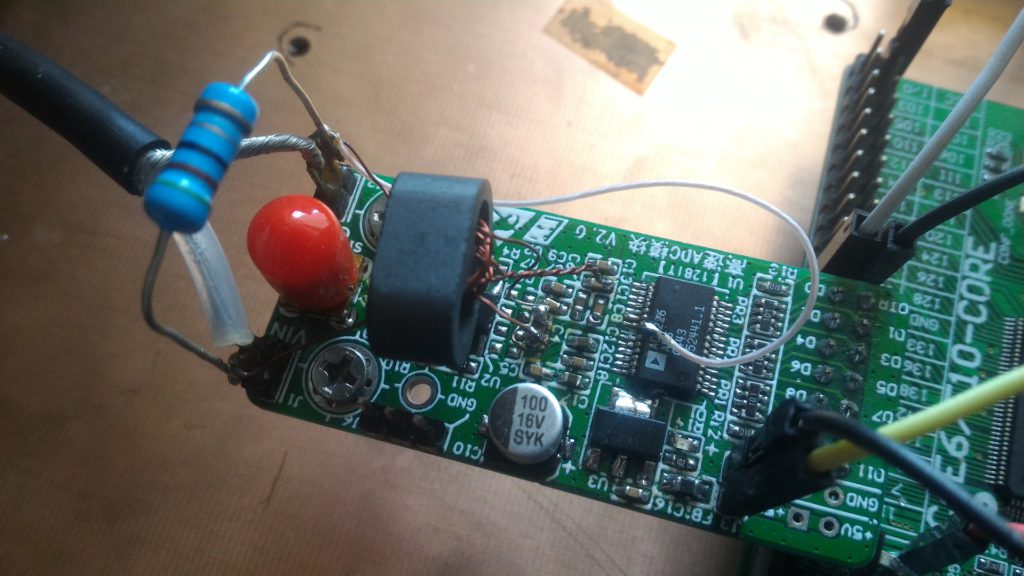

Наконец-то нашёл трансфлюктор и перемотал входной трансформатор. 6 витков скрученного провода, отвод вторички от 3-го витка.

Также нога MODE отпаяна от VDD и посажена на землю (белый провод). Тем самым мы переключаем АЦП в режим singed(знаковых) значений, и нулевое значение становится нулём, а не 2047.

Первичка зашунтирована 50омным резистором.

Вторичка подключена через 2 резистора по 22 ома.

Также, выход на ЦАП переработан на разрядность в 24 бита, немного скорректированы фильтры для лучшей компенсации зеркального канала.

Ссылка на исходники.

Полезные статьи:

- http://24dx.ru/forum/viewtopic.php?f=16&t=2519&start=10

- http://www-users.cs.york.ac.uk/~fisher/mkfilter/

- http://www.panoradio-sdr.de/ssb-demodulation/

- http://k6jca.blogspot.ru/2017/03/an-fpga-sdr-hf-transceiver-part-2-fpga.html

- http://www.microtelecom.it/ssbdex/ssbdex-e.htm

- http://k6jca.blogspot.ru/2017/02/sdr-notes-weaver-modulation-and.html