Небольшие доработки и исправление ошибок

+HARDW: Пересчитан PLL фильтр DAC (номиналы): C36, C37, R44

Повышена стабильность генерации VCO для интерполятора.

+FPGA: Улучшена точность TCXO коррекции

А также скорость захвата ФАПЧ.

+FPGA: Увеличена частота дискретизации ЦАП

Теперь она составляет 199.68мгц

+STM32: Улучшение качества FM модуляции

+STM32: TUNE в режиме FM даёт тоновый сигнал

+STM32: Исправлена ошибка ручного усиления

+STM32: Исправление мелких ошибок

+STM32: FFT стал менее размытым при смене частоты

+STM32: Выведено меню Services

В котором далее будут размещаться все инструменты, пока там содержится только анализатор спектра.

+STM32: AGC учитывает особенности человеческого слуха (K-Weighting)

Теперь AGC даёт одинаковую субъективную громкость не смотря на моду и ширину полосы. Единицы измерения громкости — LKFS.

+STM32: Улучшена работа цифрового шумоподавителя (DNR)

+STM32: Исправлены щелчки при переключении полосы пропускания

+STM32: Улучшено управление двойным приёмником

+STM32: Доработан Noise Blanker

+STM32: Оптимизирована скорость работы LCD

+STM32: Доработан AutoGainer

Все идеи, баги, пожелания, правки прошивки, прошу оформлять через заявки в репозитории https://github.com/XGudron/UA3REO-DDC-Transceiver/issues

Там можно их обсуждать, контролировать и отмечать выполненные.

Присоединяйтесь к телеграмм-каналу, посвящённому SDR радио https://t.me/SDR_Radio

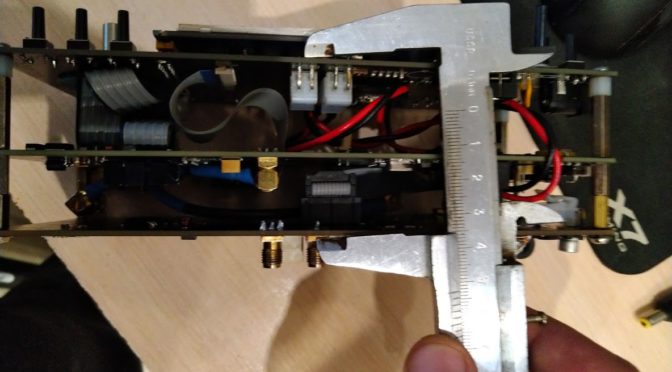

Подробное описание трансивера

Архив проекта версии 2.0.1

Репозиторий проекта на GitHub

Архив статей по проект

Спасибо Дмитрий за Ваше старание!!!!

Спасибо и Вам, за поддержку! очень приятно, что проектом интересуются.

Ждем 7″ стационарного.