Очередное обновление проекта.

+HARDW: Новая дополнительная плата-расширение с ФНЧ фильтрами. Thx Тихомир

+HARDW: RF-UNIT: изменение номиналов C38 и C80 с 1n до 100n — улучшение АЧХ на 160/80м

+HARDW: RF-UNIT: изменение номиналов L39, L47, R32, R46, C111, C81 и тока покоя оконечника — улучшение линейности на всех бендах

+HARDW: MOTHERBOARD: исправление зазоров и настроек слоёв, теперь плата отображается в JLCPCB предпросмотре. Thx R7KBI

+HARDW: Новая, перерисованная схема от R7KBI (в папке Scheme/ALTIUM_DESIGNER/R7KBI), намного более привычная для Русских пользователей

+FPGA: Оптимизация и исправление ошибок

+STM32: Оптимизация кода

+STM32: Доработка кода вывода FFT

+STM32: Водопад стал более плавным при изменении частоты

+STM32: Доработан процесс выключения

+STM32: Отрезаны неиспользуемые части FFT спектра

+STM32: Режим линзы для FFT

+STM32: Режим 3D FFT

+STM32: Очистка буффера TX при переходе в режим приёма

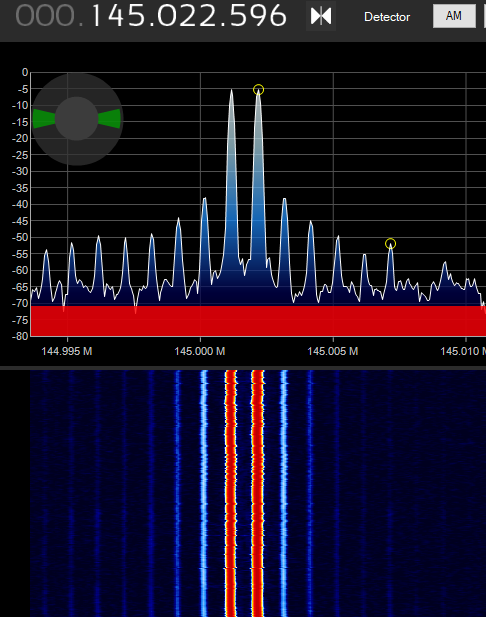

+STM32: Поправка на КСВ метр для 2м диапазона

+STM32: Исправление ошибок, Thx RN4HAQ

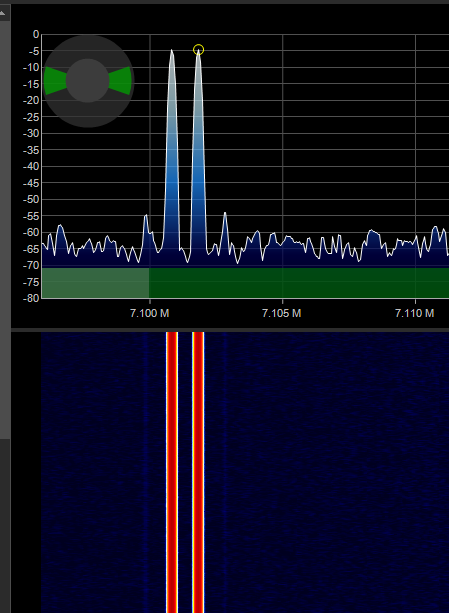

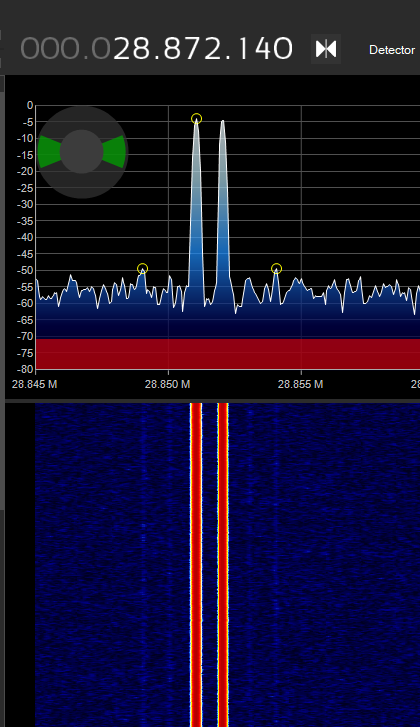

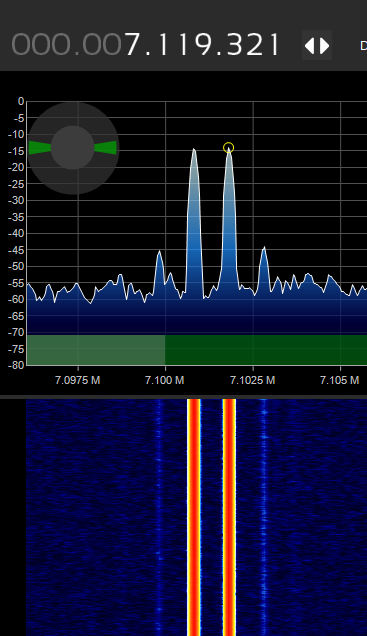

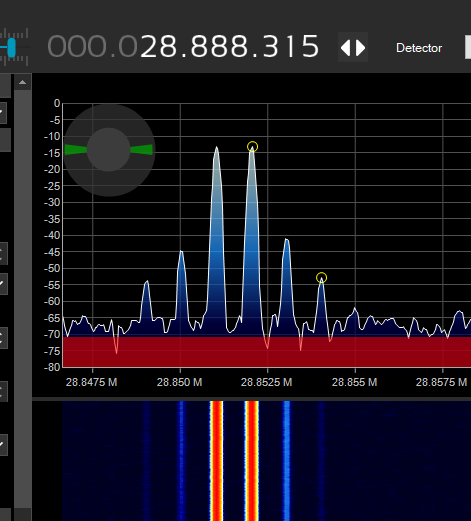

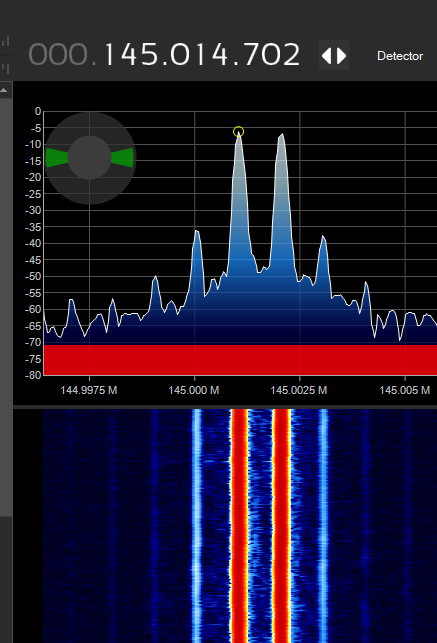

Также проведены замеры IMD3 после ЦАП с драйвером, и после усилителя (без ФНЧ, на нагрузку).

ЦАП+Драйвер:

После оконечника:

Все идеи, баги, пожелания, правки прошивки, прошу оформлять через заявки в репозитории https://github.com/XGudron/UA3REO-DDC-Transceiver/issues

Там можно их обсуждать, контролировать и отмечать выполненные.

Присоединяйтесь к телеграмм-каналу, посвящённому проекту https://t.me/TRX_Wolf

Подробное описание трансивера

Архив релизов проекта

Репозиторий проекта на GitHub

Архив статей по проекту