В этой части займёмся доработкой АЦП и подключим аудио-кодек WM8731.

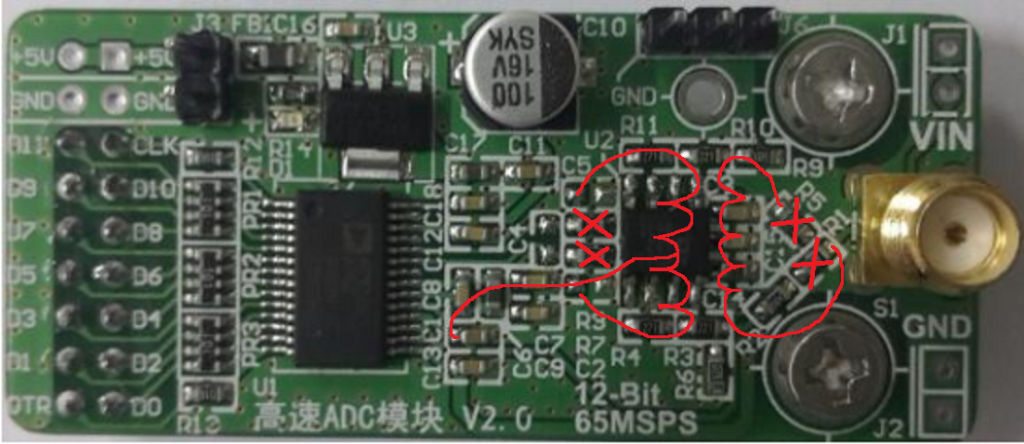

Купленный в китае модуль AD9226 предназначен для измерения напряжений от -5 до 5 вольт, что явно в избытке для антенных напряжений в несколько десятков микровольт.

Для работы с ВЧ напряжениями необходимо отключить операционный усилитель на входном каскаде и на его место включить широкополосный трансформатор 1к1 с центральным отводом.

Отключаем 2 резистора по выходу операционника и 2 резистора по его входу. Центральный отвод вторичной обмотки подключаем к источнику опорного напряжения.

Трансформатор надо намотать на небольшом габаритном бинокле, но у меня его не нашлось — взять обычное ферритовое колечко неизвестной проницаемости. Работает хорошо, но собирает много помех, буду переделывать и экранировать.

Я использовал по 10 витков на каждой из обмоток, отвод вторички с 5го витка. Это нельзя назвать идеальным рецептом — буду продолжать эксперименты когда найду ферритовый бинокль.

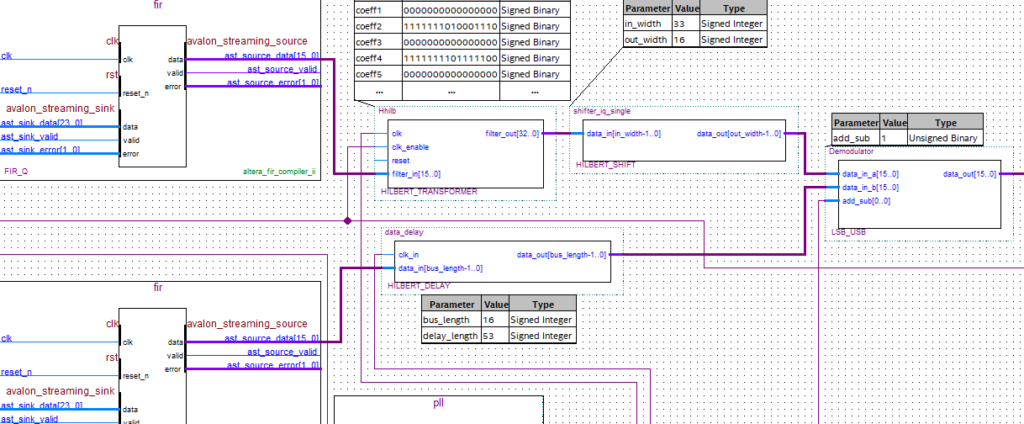

Далее вся НЧ часть была переведена на 16ти битную разрядность, для этого пришлось пересчитать преобразователь Гильберта используя математический пакет MatLab и его инструмент Filter Design HDL Coder.

Исходный файл фильтра лежит в исходниках проекта, для его открытия можно воспользоваться командой Matlab’а «filterbuilder(Hhilb)».

В итоге получаем следующую цепь

Теперь мы готовы к подключению аудио-кодека WM8731.

Работа с кодеком состоит из 2-х частей:

1. по шине I2C необходимо настроить аудио-кодек (задать громкость, частоту дискретизации, фильтры и прочее) и включить его (например во время приёма мы отключаем АЦП и включаем ЦАП, и далее наоборот. Всё это необходимо для экономии энергии, работать модули могут одновременно).

2. по шине I2S/DSP необходимо передать/принять звуковой потом необходимой дискретизации.

В данный момент в проекте реализован только ЦАП модуль, он подключается следующим образом:

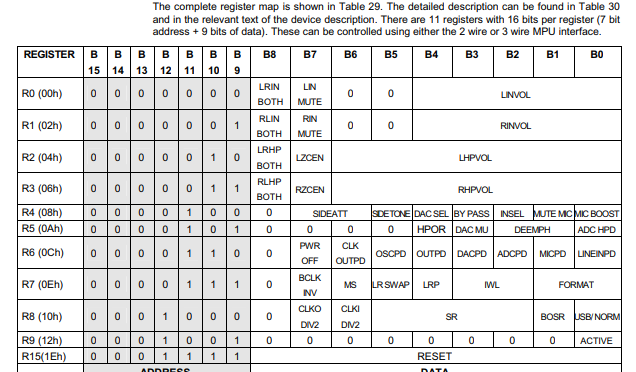

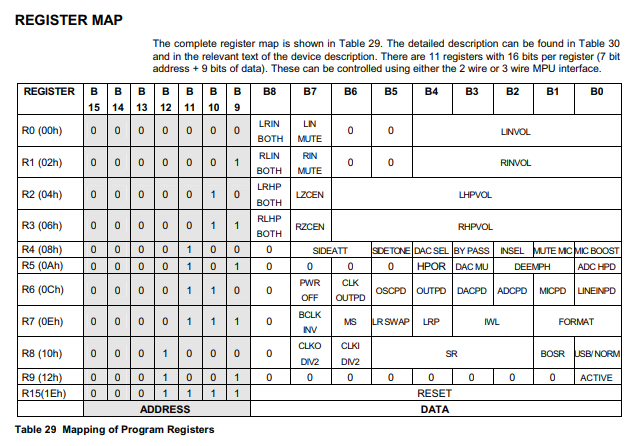

Все настройки зашиты в код.

Сами же настройки перечислены в Datasheet’е модуля и легко поддаются переводу, ссылку на него оставлю ниже.

Итогом данных доработок является очень хорошая чувствительность приёмника, сравнимая с настольным трансивером. А также хорошее качество звука, обеспечиваемое аудио-кодеком.

Ссылка на архив с проектом.

Полезные ссылки и материалы, используемые в проекте:

- http://we.easyelectronics.ru/Radio/prostoy-cifrovoy-radiopriemnik-chast-3.html

- http://www.cqham.ru/forum/showthread.php?35923-DDC-DUC-%F2%F0%E0%ED%F1%E8%E2%E5%F0-%F1-%E8%ED%F2%E5%F0%F4%E5%E9%F1%EE%EC-Ethernet-%E8%E7-%EC%EE%E4%F3%EB%E5%E9-%F1-%C0%EB%E8&p=1516500&viewfull=1

- http://r4n.su/?page_id=777

- https://geektimes.ru/post/258810/

- https://www.rockbox.org/wiki/pub/Main/DataSheets/WM8731_8731L.pdf

- http://we.easyelectronics.ru/plis/i2s-v-fpga-na-verilog.html

- http://www.dsioffe.narod.ru/myquartus/compilation/compilation.htm

- https://github.com/emard/vhdl_phoenix/blob/master/rtl_dar/wm8731_dac.vhd

- https://www.mathworks.com/videos/introduction-to-filter-design-hdl-coder-68761.html

- http://www.cqham.ru/forum/showthread.php?37592-%C1%FE%E4%E6%E5%F2%ED%FB%E9-%E4%E2%F3%F5%EA%E0%ED%E0%EB%FC%ED%FB%E9-%EC%EE%E4%F3%EB%FC%ED%FB%E9-DDC-DUC-%CA%C2-%D3%CA%C2-%CF%D7&p=1521627&viewfull=1

Заменялись ли чувствительность, ДД, избирательность по соседнему каналу, подавление нерабочей боковой?

Какой, примерно, бюджет устройства?

Проект в активной фазе развития, то одно экспериментирую, то другое, сейчас занимаюсь переводом всех цифровых фильтров на сторону STM32 микропроцессора, скоро буду АЦП менять, поэтому что-то измерять даже смысла пока нет (да и приборов пока не нашёл для этого). Я думаю какие-то характеристики и цену выложу ближе к более-менее рабочему прототипу, а не макетной плате с торчащими проводами.

Почему решили поменять АЦП? Какой АЦП планируете применить? Также делаю SDR, хотелось бы применить АЦП 14bit, но готового модуля на али не нашел, думаю AD9444 подойдет, но к ней надо будет делать плату.

Хочется большей разрядности и частоты семплирования (хочу применить TCXO кварц 96мгц, а не тактировать от PLL FPGA), также копаю в сторону 14битной версии, на али по приемлемой для меня цене нашёл AD9640ABCPZ-105.

Плату тоже придётся делать самому, но в данный момент и микросхема никак не доедет даже, зависла на таможне уже как месяц.

Я к тому, стоит ли начинать собирать комплектующие, рисовать плату и прочее. Типа стартануть с базового варианта. Вот и хотелось узнать, что базовый вариант себе позволяет.

Дмитрий, зачем вы в линии задержки добавляете лишних 2-3 такта?

Я пробовал делать по теории (Кол-во ступеней — 1)/2 получается хуже.