Обзор изменений и доработок, произошедшие с проектом.

Первым делом хочется поблагодарить всех радиолюбителей и интересующихся за внимание к проекту, это подпитывает энергией заниматься им дальше, а не выкинуть из окна))

Во вторых хочется сказать, что я не великий специалист в области проектирования радиоэлектроники, и не экспертный знаток FPGA/STM32. Проект больше носит обучающую и экспериментальную миссию, в нём постоянно что-то меняется, переделывается, и ранее затраченные деньги могут оказаться потраченными зря. Если Вам интересен полноценный хороший трансивер, то рекомендую Вам сборку аналогичных проектов, например трансивера «Аист» или подобных с аналогичной элементарной базой.

Если у Вас мало опыта программирования на STM32, FPGA, и умения пользоваться паяльником, а главное — и не собираетесь этот опыт получать — этот проект не для вас.

Предыдущая статья по проекту версии 1.0.

Итак, что появилось нового в версии 1.1:

+Прошивка FPGA адаптирована под новую версию Quartus 18.1. Из планов полный отказ от проприетарных платных модулей, чтобы облегчить требования лицензии.

+Библиотека прошивки STM32 (STM32Cube FW_F4) обновлена до версии 1.24, где исправлено много багов. Но, к сожалению, досих пор не исправлен баг с инициализацией I2S, что требует модификации файла библиотеки для её исправления. Все подробности есть в файле main.c — там прописано в каком файле какую строчку заменить на другую. Это требуется при повторной генерации проекта через STM32CubeMX, для дальнейшей работы править файл не нужно.

+Реализован UART интерфейс для отладки через USB порт, включается он в functions.c. В планах добавить туда же CAT интерфейс. Для корректной работы требуется удаление подтягивающего резистора линии USB D+ R21 на 1.5K на плате STM32. Это даст возможность рестарта USB устройства при перепрошивке, а не только при включении.

+В модуле AD9226, в дополнение к статье, изменено опорное напряжение с 2 вольт до 1го. Что по сути дало увеличение чувствительности в 2 раза, УВЧ теперь требуется только при очень слабых сигналах, но начинает требовать аттенюатор при прослушивании близлежащих мощных станций на хорошую антенну.

+Доработки FFT (вывод квадратичного значения), оптимизация водопада.

+Оптимизация кода работы с LCD дисплеем, убрал некоторые искажения звука, и другие мелкие баг-фиксы.

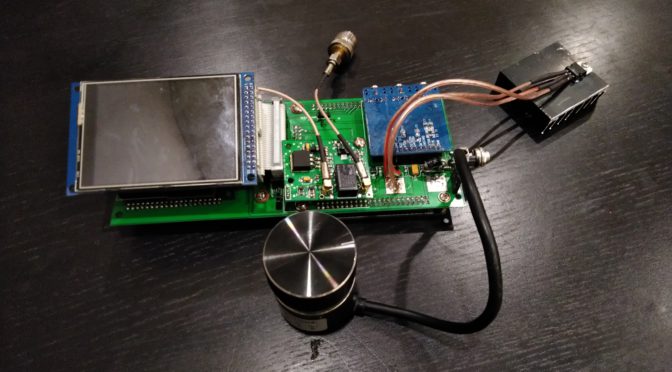

+И самое главное — проект избавился от тонны проводов и приобрёл свою «материнскую» плату, сохранив преимущества модульности. Плата была заказана на JLCPCB и вышла примерно 1500рублей, плата предусилителя и ЦАП заказана там же, все файлы есть в архиве с проектом и репозитории.

Качество проектирования платы может быть довольно топорным, но вполне рабочей для первых экспериментов, в любом случае, файлы проекта открыты и доступны для модификации «под себя».

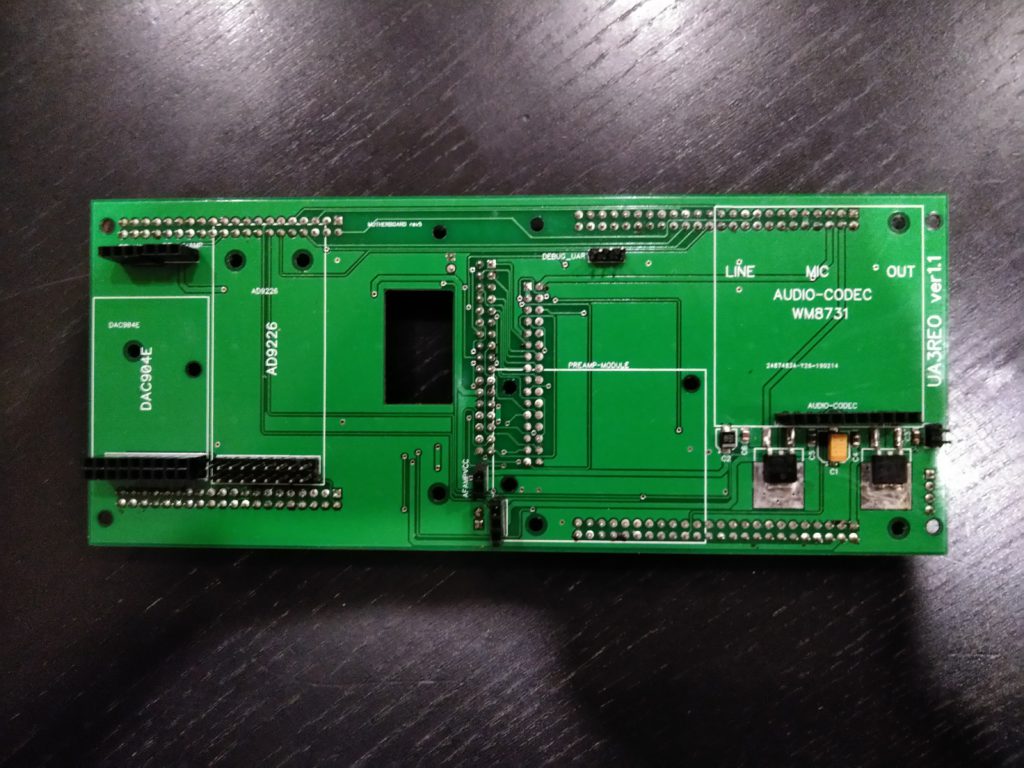

Пустая плата выглядит так (на ней было найдено несколько косяков, в файлах проекта лежит уже исправленная версия):

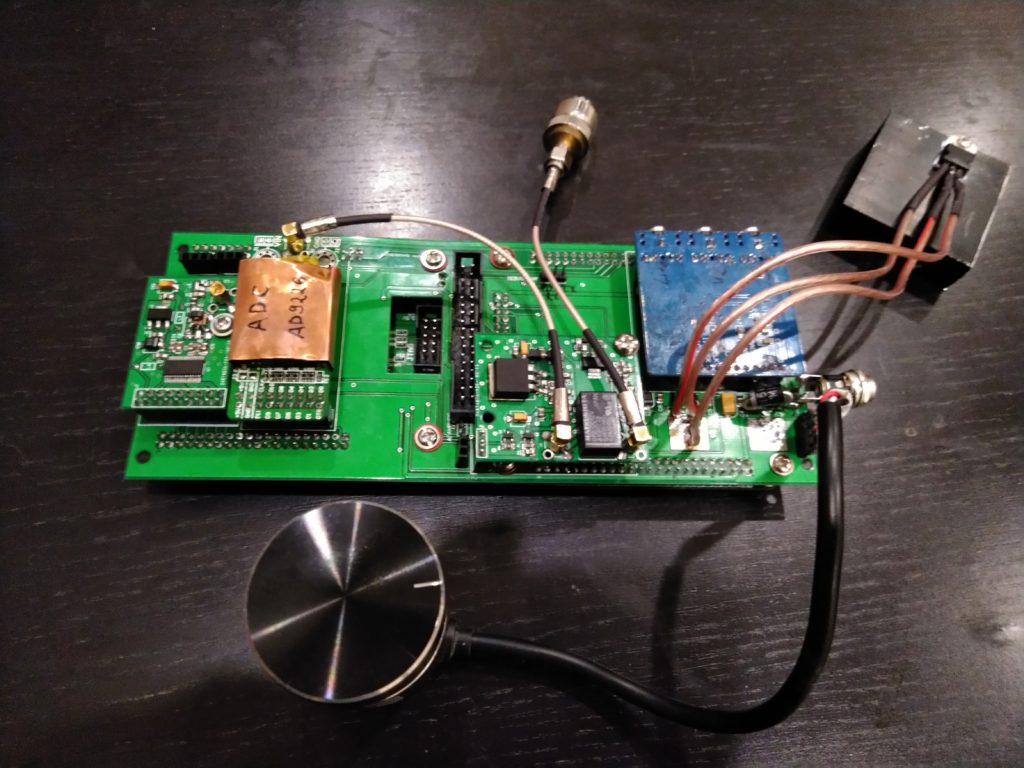

На неё монтируются IDC и PLS разъёмы, также видно что я использовал стабилизаторы 7812 и 7805, монтируемые прямо на плату, но эксперимент не удался, нагрев слишком большой, пришлось вынести 7805 на радиатор, а 7812 заменить на диод шотки от переплюсовки. Всё равно в 7812 особого смысла не было. Если кто-то посоветует импульсный DC-DC преобразователь, который можно использовать в радиотрактах (с низким уровнем шумов) — буду признателен.

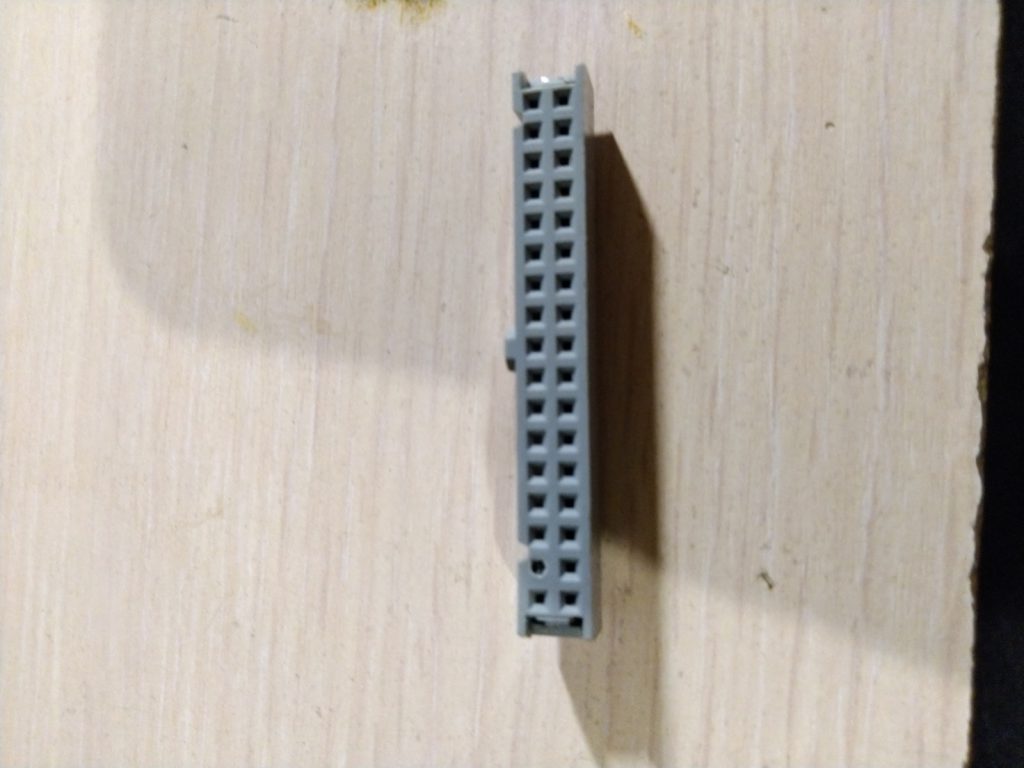

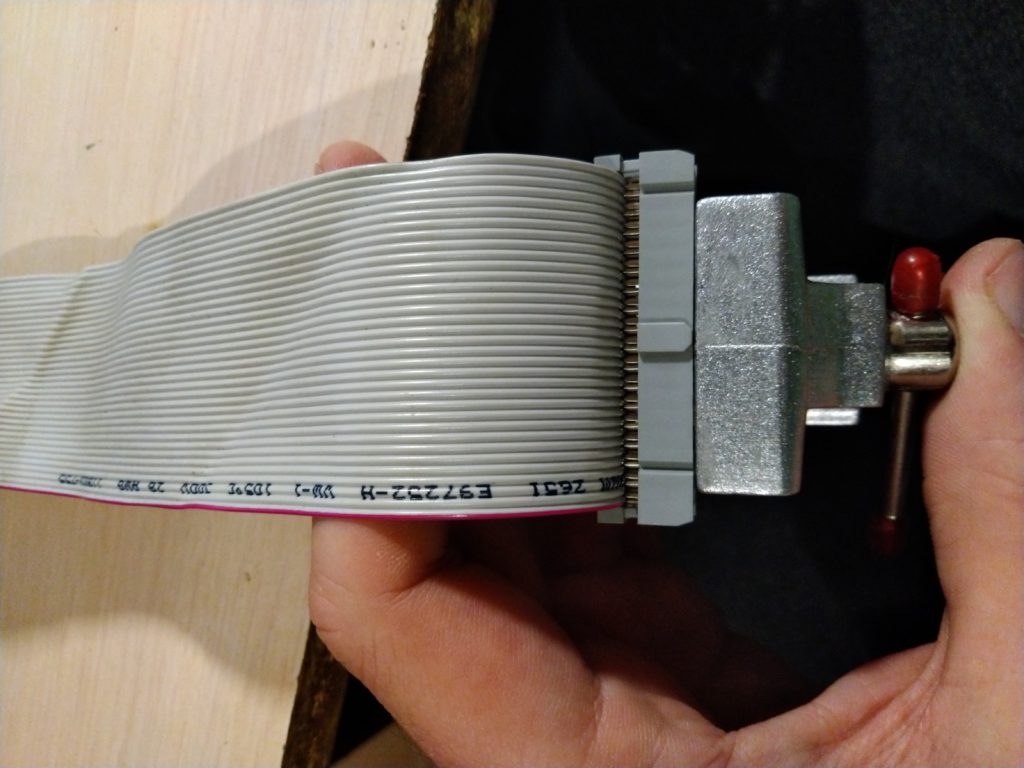

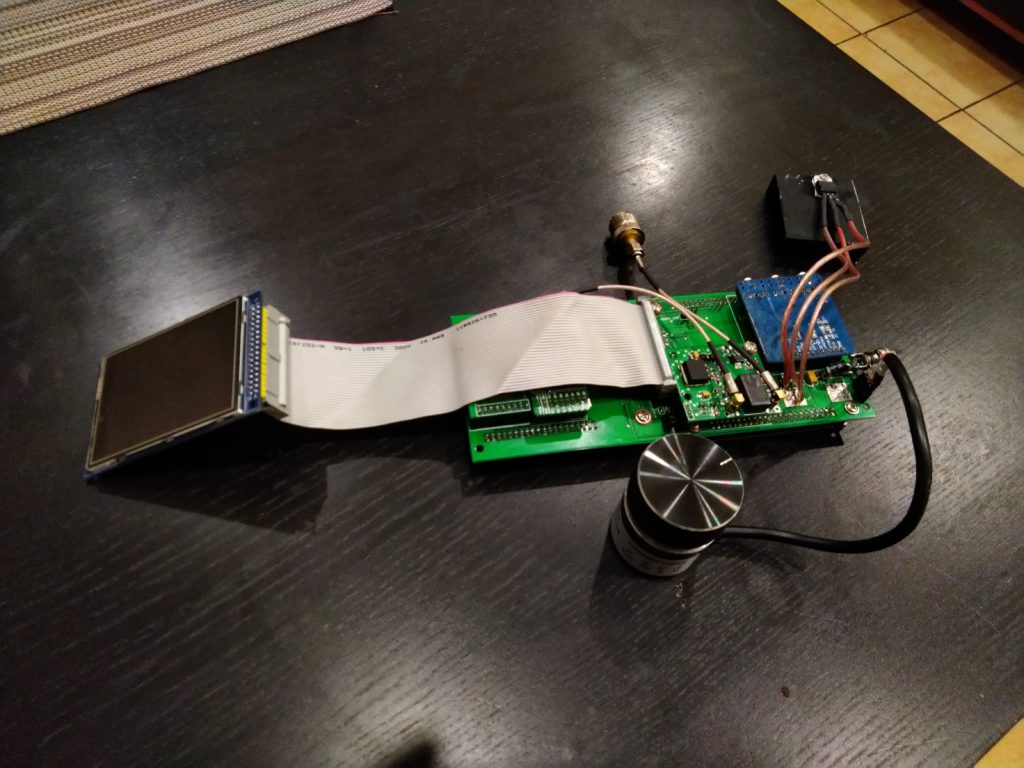

Также, шлейф LCD перекочевал на обратную сторону платы для более удобного подключения. Сам шлейф взят от FDD дисковода, а заглушка удалена небольшим сверлом (сам контакт там имеется).

Так как шлейф FDD имеет «перевёрнутый» участок, пришлось пересобрать один из разъёмов, для этого идеально подошли тиски, которые позволяют равномерно проколоть шлейф.

На тыльную сторону платы устанавливаются модули FPGA и STM32.

Для распределения тактового сигнала с генератора на АПЦ и ЦАП, через сопротивление в 56ом, выведен на неиспользуемую ногу платы FPGA.

На лицевой стороне монтируются платы ЦАП, АЦП, предусилителя и аудио-кодек. Платы разведены под ВЧ разъёмы SMA, я же применил MMCX, мне они показались более подходящими для кросс-платных соединений. Можно просто припаятьRG-174/RG-178 кабель напрямую к платам.

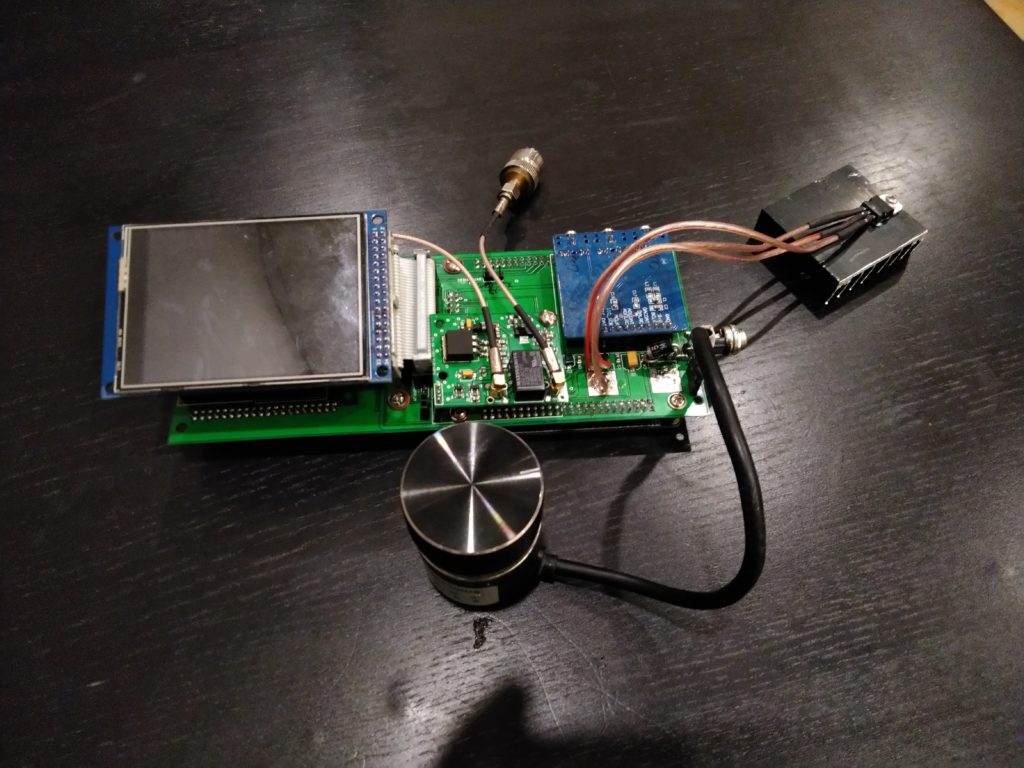

Ну и фото итогового «бутерброда»:

Файлы проекта доступны в 2х версиях (в архиве на момент публикации, и в репозитории github, постоянно обновляемые), в них включены файлы и исходные коды прошивок, даташиты, смета, схемы и чертежи плат.

С наскоку одолеть новый релиз не удалось 🙂 Под свое железо перевел, но начал просто адски глючить валкодер, в качестве которого использую механический энкодер, но заметил, что если данные от ПЛИС не поступают, работает он прекрасно (т.е. пока процессор разгружен), видимо что-то с приоритетами прерываний у меня не так. Еще водопад не отображается, наверно, пропустил что-то. А на 1.0 ну прямо совсем хорошо работает, и передача и прием, вернулся пока на него, потом еще поищу, где что я упустил.

Добрый вечер!

Возможно что-то с распиновкой упустили, из-за перевода проекта на плату многое пришлось поменять.

Для FCMS Extended mode точно должен быть disabled? У меня картинка появилась только при enabled и вводе старых таймингов.

Я убрал потому-что работает и без него) и тайминги не дают лагов. Наверное от длинны и качества шлейфов зависит.

Добрый день! Не найдутся схемы для остальных блоков? Хочеться взглянуть.

Здравствуйте. Опубликовал отчет о постройке трансивера по Вашему проекту в соответстующей теме на cqham

Аркадий, спасибо Вам!

http://www.cqham.ru/forum/showthread.php?38419-DDC-SDR-%EF%F0%E8%B8%EC%ED%E8%EA-%E8-DDC-DUC-%F2%F0%E0%ED%F1%E8%E2%E5%F0-%EE%F2-UA3REO&p=1621875&viewfull=1#post1621875

Доброго времени суток. У вас найдутся схемы модулей FPGA, STM32, кодека? Можно взглянуть?

Приветствую! Эти модули — готовые, куплены в китае, ссылки есть в файле со сметой.

Схема STM32 модуля есть в PDF формате в папке Datasheets