С трансивера была проведена первая полноценная радиосвязь, поэтому проект можно считать успешным, и остальные доработки будут только наращивать функционал.

Релиз является итогом работы по следующему циклу статей:

- Строим цифровой DDC SDR приёмник своими руками (часть 1)

- Строим цифровой DDC SDR приёмник своими руками (часть 2)

- Строим цифровой DDC SDR приёмник своими руками (часть 3)

- Строим цифровой DDC SDR приёмник своими руками (часть 4)

- Строим цифровой DDC SDR приёмник своими руками (часть 5)

- Как перепаять TQFP 144 микросхему с теплоотводом (замена EP4CE10 на EP4CE22)

- Строим цифровой DDC SDR приёмник своими руками (часть 6)

- Строим цифровой DDC/DUC трансивер своими руками (часть 1)

- Строим цифровой DDC/DUC трансивер своими руками (часть 2)

- Строим цифровой DDC/DUC трансивер своими руками (часть 3)

- DUC-DDC Трансивер UA3REO: доработка кодека WM8731

- DUC-DDC Трансивер UA3REO: доработка АЦП AD9226

- DUC-DDC Трансивер UA3REO: уменьшаем джиттер

- DUC-DDC Трансивер UA3REO: боремся с искажениями звука

- DUC-DDC Трансивер UA3REO: упаковываем в корпус

Основное, что есть в планах на будущее:

- Новый 2-х канальный АЦП на 14 бит, позволит не только улучшить динамику приёмника, но и реализовать интересные штуки вроде фазового подавления помех.

- Переделать усилитель на более экономичный.

- Разработать единую плату, и избавится от кучи проводов.

- Реализовать УКВ и FM режимы.

- Подключить тактование на 96мгц.

- Реализовать стриминг данных по WiFi на компьютер.

и многое-многое другое.

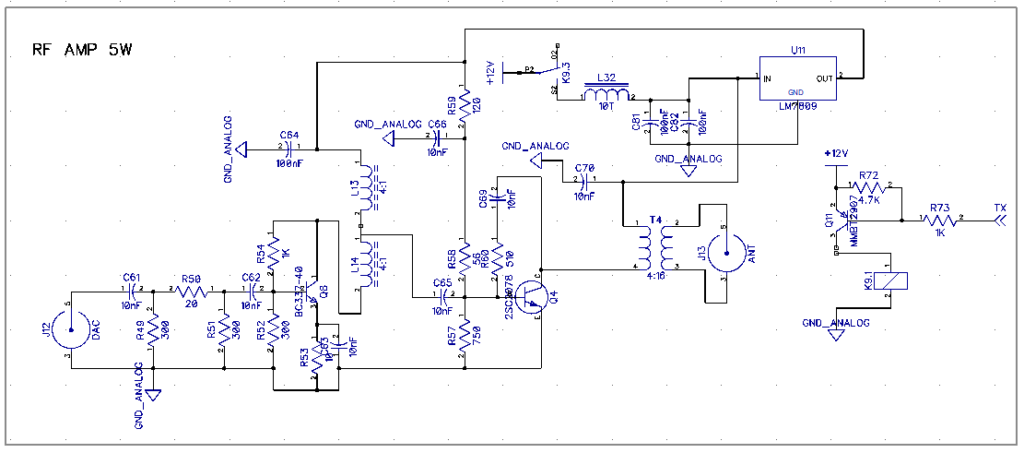

Собственно версия 1.0 была реализована за счёт применения миниатюрного усилителя мощности класса А на 5ватт, повторять который я не рекомендую из-за низкого КПД, но очень хотелось уже пустить аппарат в бой, собран по простейшей схеме на куске платы от китайского усилителя, работа которого мне не сильно понравилась.

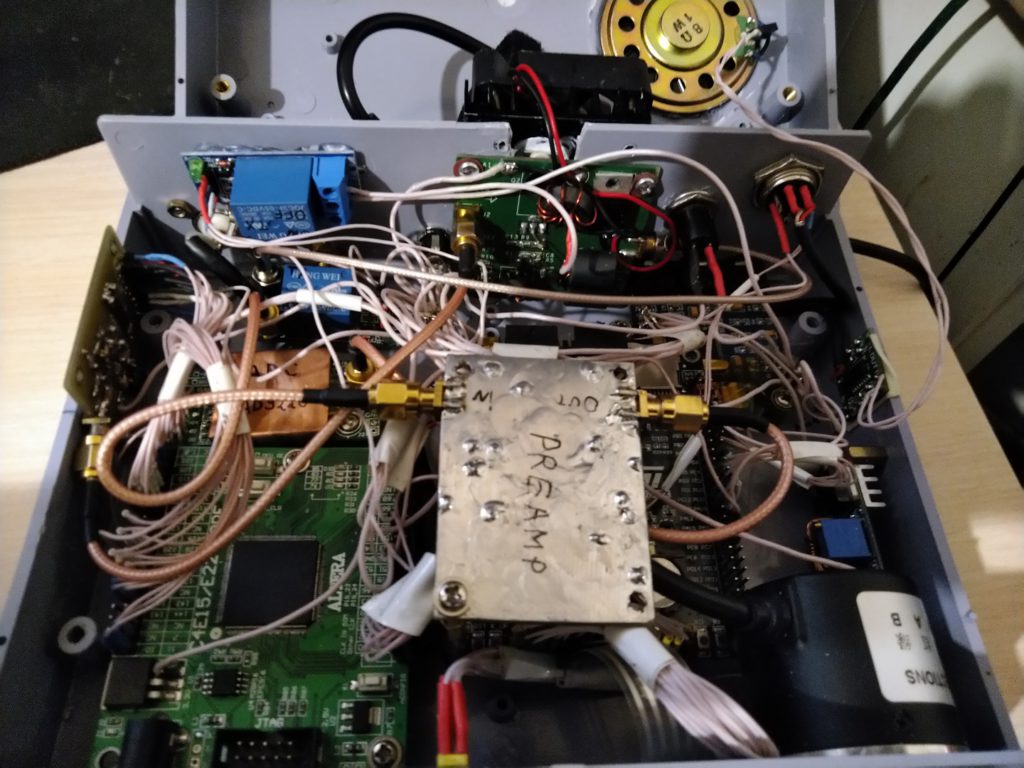

Всё упаковано в основной корпус, и теперь это полный хаос из проводов, как только закончу эксперименты с новым АЦП — буду реализовывать отдельную единую плату, где размещу все элементы.

За контроль работы отдельное спасибо моему отцу, UA3RGQ, главному вдохновителю на этот подвиг.

Ну и видео работы на приём, на передачу мало чем отличается))

Файлы проекта версии 1.0 доступны тут.

Здравствуйте. Обратил внимание на расхождение в схеме diptrace и файле stm32cube, разница в шине между fpga и stm32, а также в подключении кодека. На какой из вариантов ориентироваться?

Приветствую! лучше ориентируйтесь на stm32cube, в схеме могут быть ошибки, отловлю и исправлю к следующей версии.

Схемы модулей остались прежними? Раньше они были в общей схеме, а теперь остались лишь распиновки. К слову, поскольку i2s_clock берется от fpga, кварц в кодеке больше не нужен?

Да, схемы модулей не изменились. Кварц да, не нужен, с ним только хуже звук получился.

FPGA_Audio_Buffer_Q[0] и FPGA_Audio_Buffer_I[0] пустые, с чем это может быть связано?

Выведите значение переменной FPGA_samples, больше нуля? (в файле stm32f4xx_it.c)

И проверьте поступает ли тактовый сигнал из FPGA (прерывание EXTI15_10_IRQHandler)

Оказалось, забыл переставить тактирование на АЦП с генератора ) Теперь на экране следующее: водопад пустой, область fft полностью красная, в рандомных местах проскакивают разноцветные палки. FPGA_samples ~47200, EXTI15_10_IRQHandler срабатывает. FPGA_Audio_Buffer_Q[0] и FPGA_Audio_Buffer_I[0] содержат околонулевые значения.

Возможно дело в АЦП.

В FPGA код добавьте компонент Altera In-system sources&probes разрядностью в 12 бит, и подсоедините его ко входу с АЦП.

Соберите проект и закиньте в плату.

Далее откройте файл Debug_probes.spf и по JTAG получите значения, летящие из АЦП. Тип данных — Two’s complement (обязательно). Посмотрите какие цифры прилетают.

У меня они в диапазоне от -1500 до +1500 при включённом предусилителе, и -200 +200 без него, без антенны близки к нулю.

Проверил АЦП откатом к предыдущему проекту, радиопереговоры на 80м диапазоне слышны. В чем тут проблема, не пойму пока. Попробую подключить АЦП по схеме проекта, возможно, что-то напутал со своей распиновкой.

Нет, с распиновкой ошибок не было, после подключения по Вашему варианту ничего не изменилось. Цифры смотреть надо с порядком MSB on top?

Да, MSB Top, LSB Bottom

Сейчас проверил данные с Вашими настройками — при неподключенной антенне попеременно -1152 и 1920. В проект изменений не вносил, кроме перестановки probe на adc_input и изменения ее разрядности на 12. Распиновку вчера несколько раз проверил. На модуле АЦП нога mode на земле, подтяжку к питанию по входу не делал. К слову, сделал общую плату для ЦАП и АЦП по Вашей схеме, но пока еще детали на нее не переносил.

Странные значения, у меня такие были когда Mode было притянуто не к земле, а к питанию, так было по умолчанию у китайцев.

В таком режиме значения идут в Binary режиме, а не комплиментарном, можно привести к нужному виде через вычитание из значений АЦП половины (2047 вроде бы).

Сейчас вернулся к модульному проекту с cqham, чтобы проверить работоспособность АЦП, эфир принимается. Что интересно, на питании или на земле mode, разницы ни в качестве, ни в громкости приема не заметно. Как тут пробы подключить, не знаю, схемы в проекте нет.

Кстати говоря, на том проекте распиновка АЦП обратная относительно Вашей схемы, давно еще заметил.

В даташите AD9226 просто Bit1 идёт MSB, а для FPGA нулевой бит это LSB, вообщем всё наоборот

Я имел в виду, что на Вашей схеме выход АЦП D0 идет на 1-й контакт входной шины, а на модульной с cqham — на 11-й.

Нет у меня больше идей, почему у меня не может работать Ваш проект (ПЛИС часть). Сейчас перенес АЦП на плату, разведенную по Вашей схеме, все то же самое, что было описано мной ранее. Модульный проект с cqham работает с моим АЦП, Ваш — нет.

Очень странно, особенно пугают данные с Probe, ведь они показывают вход на FPGA, до любого кода проекта. А если порядок подключения шины D11..D0 сделать в обратном подрядке, какие цифры будут без антенны?

Пробовал так делать, когда АЦП был на исходной плате, попробовал и сейчас. На плате с алиэкспресса данные были 20-30, на плате по Вашей схеме с подтяжкой к питанию 50-60. Такой же эффект от перемены порядка MSB и LSB в пробах. На подключение антенны реакции нет. Вечером перенесу АЦП обратно и еще раз проверю его модульным проектом. Но там как раз и вычитается 2048 из полученного значения, точнее, инвертируется крайний бит, не помню с какой стороны, при этом mode на питании.

50-60 это уже адекватно, можно оставить и посмотреть Probe на выходе с FPGA, перед отправкой в STM32, надо отловить момент где данные теряются.

В идеале числа от -2048 до 2048 преобразуются в дробные числа от -1 до 1 в STM32

Знаете, просто мистика какая-то 🙂 Переставил АЦП обратно, залил модульный проект — все прекрасно, прием присутствует. Ну, хотя бы АЦП в порядке. С Вашими проектом и схемой — ни в какую. Завтра еще раз попробую.

Решил не ждать до завтра, переделал все на Ваш проект, но с обратной распиновкой, сейчас имеем следующее: по пробам без антенны 20-30, если коснуться одного из входов АЦП, цифры скачут положительные, если другого — отрицательные. На подключение антенны реакции не заметил. Дисплей при касании входов закрашивает красным область FFT, водопад пустой.

Можете выложить свои отладочные данные из stm32f4xx_it.c, чтобы я мог сравнить с тем, как должно быть?

Временно не могу этого сделать — переделываю трансивер на единую плату, чтобы избавиться от проводов, поэтому он сейчас в полностью разобранном виде. Какие переменные интересуют? попробую по памяти описать.

Также вспомнил, что подобный баг был когда я попытался использовать компилятор Keil’а версии 6, что-то он оптимизировал в коде и он не работал. Вернулся на версию 5 (выставляется в Options for Target), с уровнем оптимизации O3 или O2 и сразу стало всё ок.

А у меня с 5-й версией откомпилированная программа виснет на этапе инициализации I2S, с 6-й такой проблемы нет. Попробую с уровнями вечером.

Да, стоит попробовать разные подтяжки на линиях в кодеке, 1кОм или 10кОм. А вот с 6й версией я даже не знаю что и делать — в одном месте программа кладёт в массив одно float32 значение, тут же с другой функции его читает — а оно другое, помогало только снижение уровня оптимизации до O1, но в итоге вернулся на 5ю версию. Не знаю как это побороть.

Зависание происходит до момента обращения к кодеку, в процедуре MX_I2S3_Init().

Пошаговой отладкой выцепил проблемный момент, файл stm32f4xx_hal_i2s.c, участок кода 312-335, выход с ошибкой HAL_I2S_ERROR_PRESCALER. Не рассчитывается делитель. Не вижу пока, где исток проблемы, инициализация такая же, как у Вас, уже и куб обновил, но считатся делитель не хочет. А с 6-й версией компилятора рассчитывается 🙂

По итогам поисков в строке 289 файла stm32f4xx_hal_i2s.c «i2sclk = HAL_RCCEx_GetPeriphCLKFreq(RCC_PERIPHCLK_I2S);» заменил на «i2sclk = EXTERNAL_CLOCK_VALUE;», после чего инициализация прошла и даже что-то начало рисоваться на экране, но все равно не то, что нужно. FPGA_samples и WM8731_DMA_samples завышены примерно в 2 раза и сильно зависят от уровня оптимизации кода, выбранного в настройках. Короче, опять что-то не то.

Попробуйте вот этот багфикс, в библиотеке HAL есть ошибка, надо один файл поправить https://community.st.com/s/question/0D50X00009XkWr4SAF/bug-report-stm32cubefwf4v1210-bug-fix-in-macro-halrccgeti2ssource

Фикс оказал такой же эффект, как и от подстановки EXTERNAL_CLOCK_VALUE, все вышеописанное не изменилось.

FPGA_samples=48700-49100

AUDIOPROC_samples=192

WM8731_DMA_state=0-1

WM8731_DMA_samples/2=48896-49152

Данные должны быть такие? При распиновке по Вашей схеме на водопаде разноцветный шум.

Да, всё так, тактование и I2S точно правильно работают. Приёма станций вообще никаких нет? даже мощных AM вещалок?

Нет, вообще ничего, на пробах ранее приведенные цифры. А как у Вас подключено тактирование к АЦП? Напрямую от генератора на плате ПЛИС? В модульном проекте с cqham клок формируется в ПЛИС, тут вообще никаких проблем с приемом, станции на 80м слышны даже без УВЧ, сигнал прямо на трансформатор подаю без полосовых фильтров.

Уточнение: у Вас — т.е. по факту на работающем устройстве, а не по схеме. Возможно, были какие-то неотраженные на схеме изменения.

Да, напрямую от генератора 50Мгц, но без УВЧ приёма почти нет, попробую затактовать от отдельного генератора, лежит на 96мгц, но уже для другого АЦП пойдёт.

Последняя надежда была на проблемы с тактированием АЦП. Очень хотелось иметь автономное устройство, но, видимо, придется довольствоваться приставкой к компьютеру. Что-ж, успехов Вам в развитии Вашего проекта, возможно, буду пытаться повторить следующие версии Вашего трансивера с другой элементной базой. 73!

А ведь похоже, что рано я стал списывать Ваш проект со счетов 🙂 Взял модуль AD9850 с ардуиной и подал с него сигнал на АЦП, и ведь появилась палка в нужном месте! Правда, звука нет, но это уже нюансы, в планах переразвести плату кодека. Также непонятно, почему такая мизерная чувствительность, ведь с модульным проектом с cqham вот только что принимал на +10 станции на 80-ке без УВЧ, а антенна у меня ооочень плохая, и изоляция у кабеля вся потрескавшаяся.

Поэкспериментировал я тут немного и решил тактовать АЦП от ПЛЛ, добавил еще 1 выход на 50МГц, чтобы исключить возможную просадку сигнала от генератора из-за повышенной нагрузки. Также добавил инверсию 12-го бита АЦП, чтобы не перепаивать модуль каждый раз при перемене проектов.

Круто! хорошие новости! насчёт чувствительности — есть подозрение что я мог ошибиться в коде FPGA.

Как снова соберу все платы воедино, надеюсь в начале марта, протестирую все узлы, посмотрю где что может теряться, возможно на этапе CIC децимации/компенсации что-то срезает.

Где-то что-то точно режется, сейчас наконец-то услышал первые звуки станций на 80м. Антенна без УВЧ, водопад пустой, периодически красный фон на весь спектр проскакивает, без AGC прием пропадает вместе с эфирным шумом.

P.S. С праздником! 🙂

Перемотал трансформатор и сделал подтяжку к питанию по входу, а также подключил УВЧ, стало совсем хорошо принимать, но лишь с AGC. Водопад отрисовывается, но заметил такую вещь, что при совсем низком уровне сигнала он закрашивается красным фоном, а на спектре высота линий не пропорциональна силе сигнала, завышена в синей части.

Принято, возьму на доработку! Если будут ещё идеи — пишите, с радостью возьму в план на развитие проекта.

Знаете, есть еще одна идея, правда, не совсем по развитию проекта, а как бы параллельным курсом — добавить режим осциллографа. Железо, по идее, более чем достаточное, лишь входную часть добавить. В любом случае буду пытаться самостоятельно что-то делать в этом направлении, как только изучу теорию немного.

Добрый день! Интересный у вас проект. У меня установлен Quartus Prime 15.1. Так вот сначала не получалось откомпилировать его из-за проблема с отсутствием сигнала .sclr.

Загрузив проект и зайдя в файл mixer.v, я попытался закрыть его. Квартус спросил, желаю ли я сохранить измененные файлы или файл (не помню точно), я ответил ДА и ,о чудо, проект стал собираться без ошибок. Сейчас проект компилируется. Правда пока нет макета, на котором можно было бы все попробовать. Надеюсь обзавестить макетом и попробовать все живьем.

Кстати я самостоятельно перерисовал в диптрейсе плату, аналогичную этой

https://ru.aliexpress.com/item/xilinx-fpga-development-board-spartan6-xilinx-spartan-6-XC6SLX45-xilinx-board-xilinx-spartan-6/967529392.html?spm=a2g0v.search0604.3.39.27774d8aMRczmP&ws_ab_test=searchweb0_0,searchweb201602_5_10065_10068_319_317_10696_453_10084_454_10083_10618_10307_10301_537_536_10902_10059_10884_10889_10887_321_322_10915_10103_10914_10911_10910,searchweb201603_60,ppcSwitch_0&algo_expid=f0b3521b-6a85-4711-bda5-fd0d4f074531-6&algo_pvid=f0b3521b-6a85-4711-bda5-fd0d4f074531&transAbTest=ae803_4

Заказал платы на JLCPCB. В результате имею работающие платы с EP4CE6/10. EP4CE22 не пробовал пока запаивать.

Спасибо вам за проект.

Евгений, RV3BJ

Интересный баг, попробую поставить такую же версию и «вылечить». Спасибо за информацию!

А не поделитесь схемой макетки FPGA? я тоже набрасывал в диптрейс, но не уверен что верно описал обвязку.

Конечно поделюсь и схемой и платой. Даже физическую плату могу прислать. Сообщите email и адрес.

Физическая есть, спасибо! а вот схема-плата будет просто замечательно, благодарю!

В понедельник 4-го марта возвращаюсь домой в Москву и сразу вышлю. Там главное это подключение выводов msel0, msel1 и msel2. Должна быть комбинация 0, 1, 0.

Также не надо забывать подключить вывод земли на днище микросхемы.

Я же верно понимаю, что УВЧ на BFG591 можно использовать и как предусилитель для DAC?

Не пробовал, но думаю что да, вполне! Я планирую OPA2674 применить для этой цели.

К нему бы дисплей 7′, с хорошим, проработанным графическим интерфейсом, получился бы шикарный аппарат. А пока даже цифры частоты напоминают о «Микро-80», или РК-86.

Трансивер постепенно приобретает законченный вид. УВЧ использую и как предусилитель, сделал коммутацию с помощью реле. В качестве корпуса использую распределительную коробку 240х195х90. Заметил такой нюанс, что в произвольные моменты трансивер может зависнуть при нажатии на TUNE, лечится только сбросом питания. Пока пишу, вызвать это не удалось ), но как помню, в отладке выдается только FPGA_samples, все остальное по нулям.

Не подтянул к земле CSB на кодеке, из-за этого он и глючил временами из-за накопления статики и смены адреса.