Очередное обновление проекта в программной и аппаратной части.

Что изменилось по сравнению с версией 1.6:

+STM32: Улучшена работа с тачпадом

+STM32: Новая более точная калибровка тачпада по 9 точкам

Китайские тачпады не отличаются большим качеством, поэтому данные, поступающие с сенсора крайне нелинейны и «заваливаются» к углам. Добавлен алгоритм, которых компенсирует эти проблемы.

+STM32: Обновление до STM32Cube FW.F4.1.24.1

И другое ПО/библиотеки, используемое в проекте, обновлено до последних версий.

+FPGA: Шина обмена с STM32 теперь использует 8 двунаправленных бит (было 2 направления по 4 бита)

Теперь шина используется более эффективно, ранее половина шины всегда простаивала. Это позволяет передавать больше информации за тоже время.

+FPGA: Изменена визуальных схема части TX

В Quartus’е перерисована передающая часть, она стала более наглядной для понимания и удобней для доработок.

+FPGA: Фильтр Гильберта перенесён в FPGA

Данный фильтр очень ресурсоёмкий, а т.к. теперь появилось место в шине и FPGA — его код был перенесён туда, что освободило STM32 для других задач.

+STM32: Оптимизация памяти FFT

Доработаны алгоритмы, что сократило использование RAM памяти для расчёта FFT.

+STM32: Разделены IIR ФВЧ фильтры для SSB и других мод

Для каждой моды можно настраивать частоту верхнего и нижнего среза отдельно.

+FPGA: Данные о максимальной амплитуде принимаемых сигналов (в т.ч. вне полосных) на выходе АЦП передаётся в STM32

Текущее заполнение диапазона АЦП передаётся в STM32 для анализа и автоматизации.

+STM32: Автоматическое управление ФНЧ, ДПФ, предусилителем и аттенюатором в зависимости от мощности сигнала на входе АЦП

Экспериментальная функция: автоматическое управление входными цепями исходя из текущего заполнения динамического диапазона АЦП.

+STM32: Улучшена работа RX AGC (устранены щелчки)

Реализована более плавная работа AGC, переписан устаревший код.

+STM32: Отключение HPF и AGC в DIGI

Для цифровых мод автоматически отключается АРУ и ФВЧ.

+STM32: Новый корректор DC составляющей

Новый фильтр качественней и быстрее срезает пик на «нулевой частоте».

+STM32: При первом запуске трансивера вызывается калибровка экрана

В EEPROM сохраняется значение, была ли проведена калибровка экрана, или это первый запуск трансивера.

+STM32: Реализация Notch-фильтра с автоматическим расчётом коэффициентов для Biquad фильтра

Добавлен Notch-фильтр для удаления узкополосной помехи, частота среза регулируется во всей полосе приёма.

+STM32: Из системного меню можно перейти в режим программирования через USB (DFU), скрипт для программирования FLASH.bat

Добавлена возможность удобной перепрошивки STM32 контроллера прямо по USB кабелю.

+STM32: Доработано системное меню

Теперь код стал более удобным для понимания и простым для дальнейшего развития.

+STM32: Базовая реализация CW декодера на алгоритме Гёрцеля

Первые эксперименты по декодированию CW прямо на экран трансивера, сейчас приемлемо декодируются только мощные сигналы, буду продолжать работу по этому направлению.

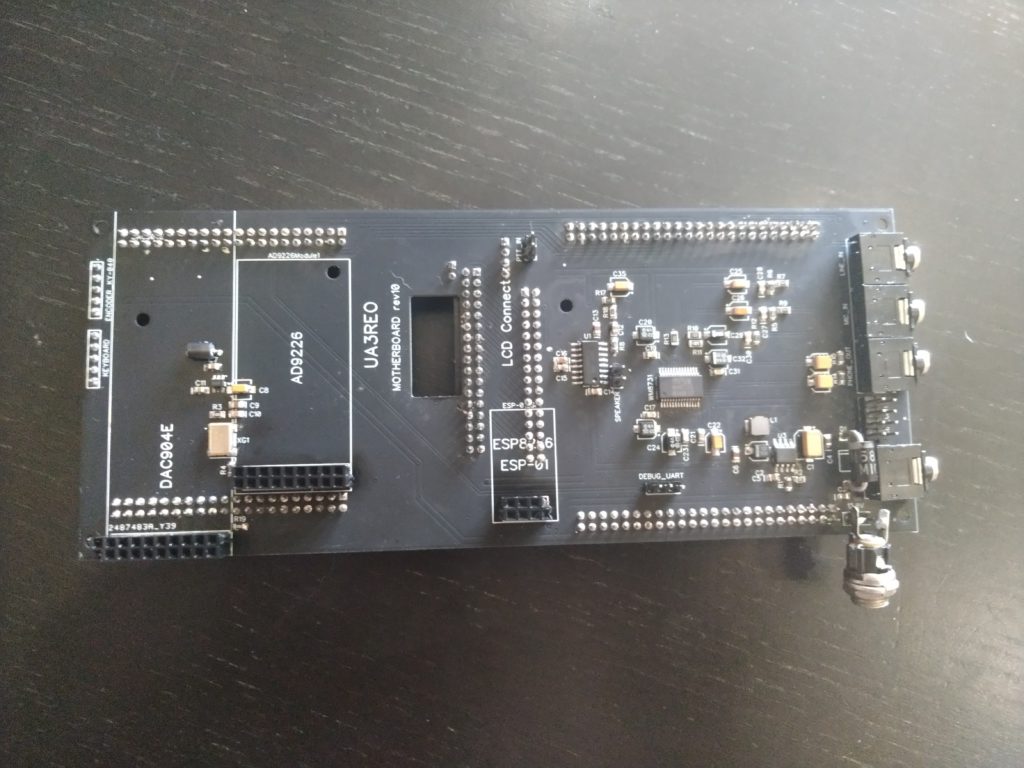

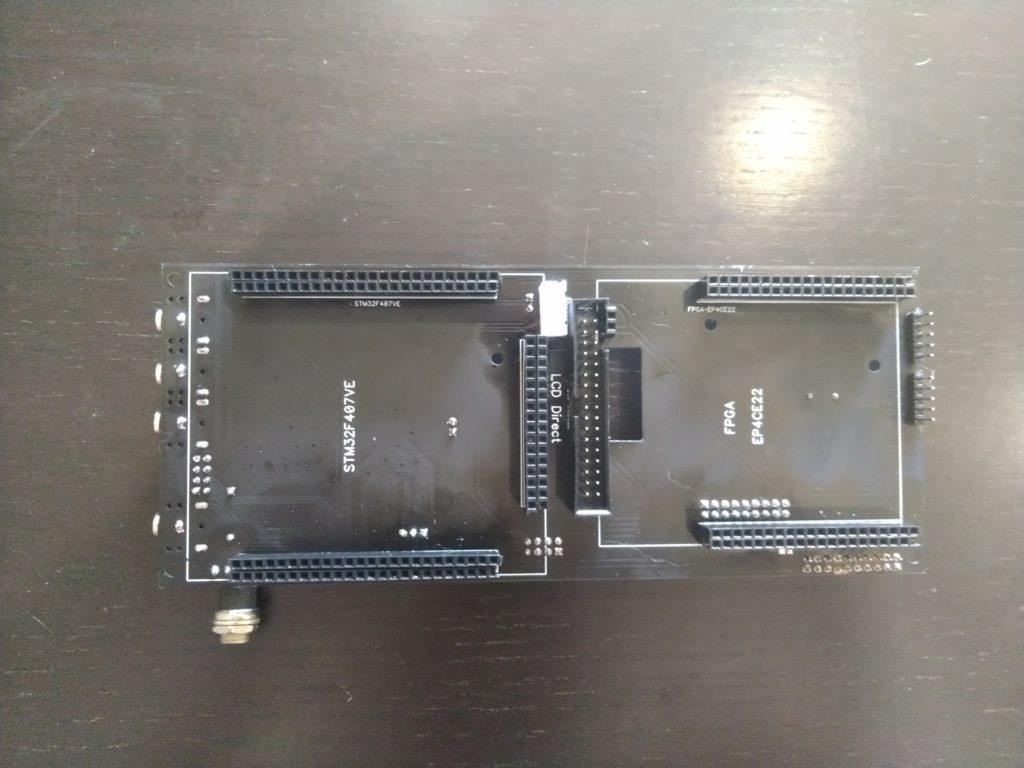

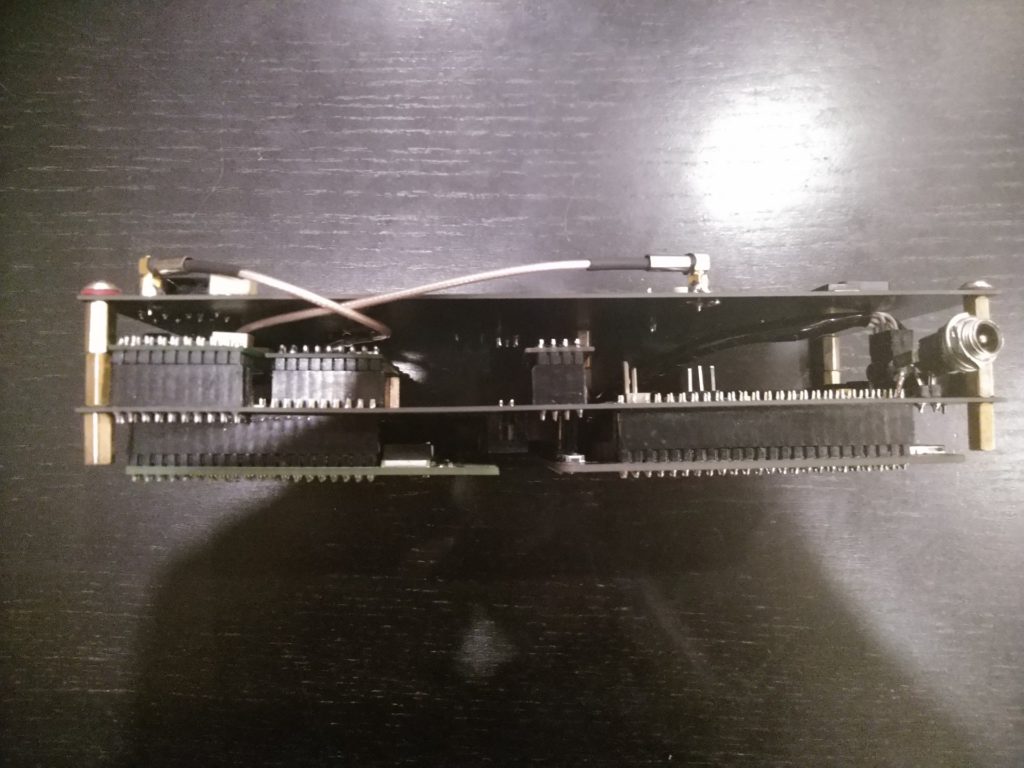

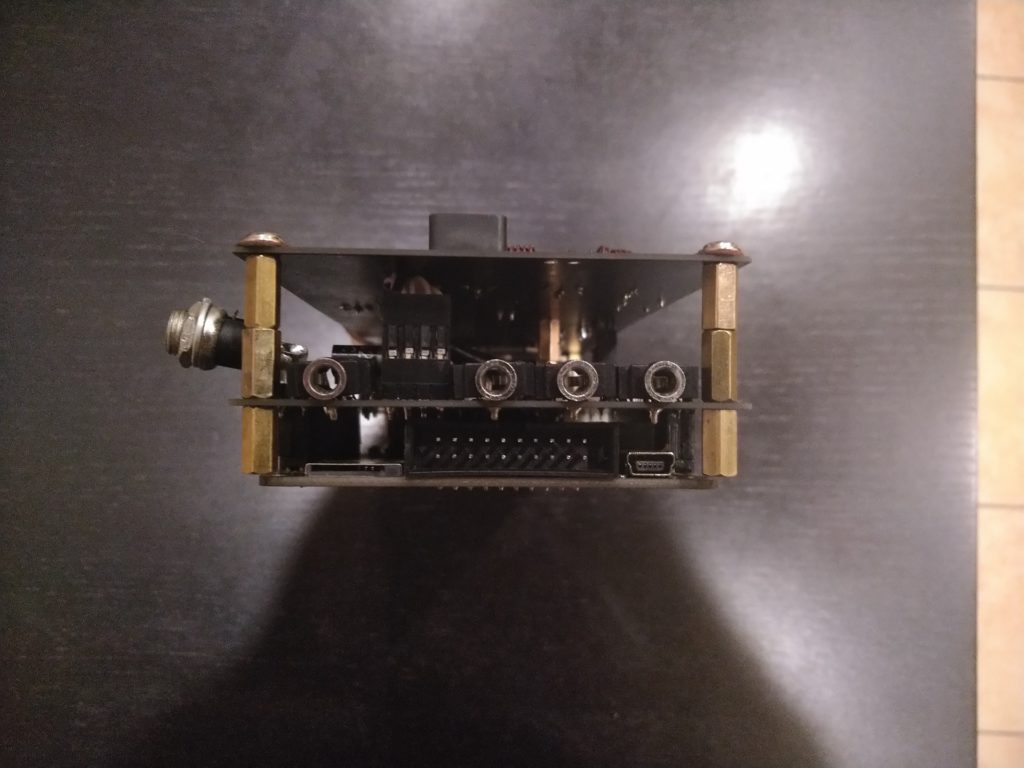

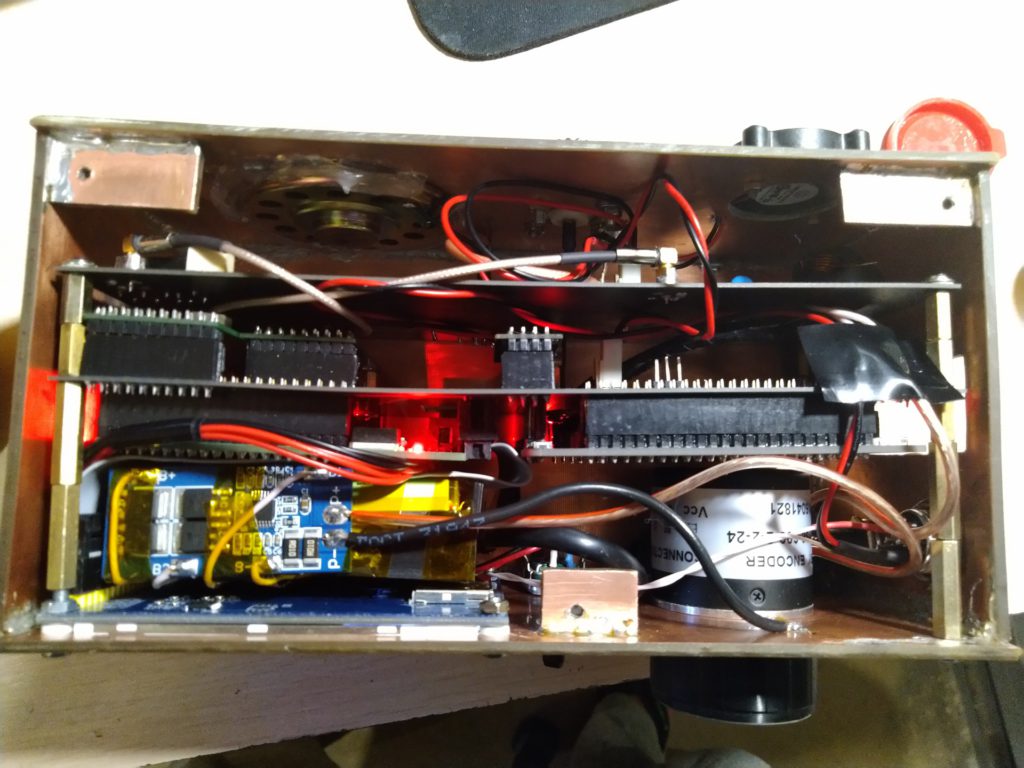

+HARDW: Новая материнская плата

+HARDW: Добавлен разъём подключения ключа с раздельными сигналами точка-тире

+HARDW: Выведены разъёмы подключения вспомогательного энкодера и кнопок управления

+HARDW: На плату добавлен разъём подключения WiFi модуля ESP-01

+HARDW: Аудио кодек переехал на материнскую плату

+HARDW: Добавлена возможность тактования ЦАП из FPGA

Обновлена схема и разводка материнской платы, добавлены новые возможности и устранены некоторые проблемы.

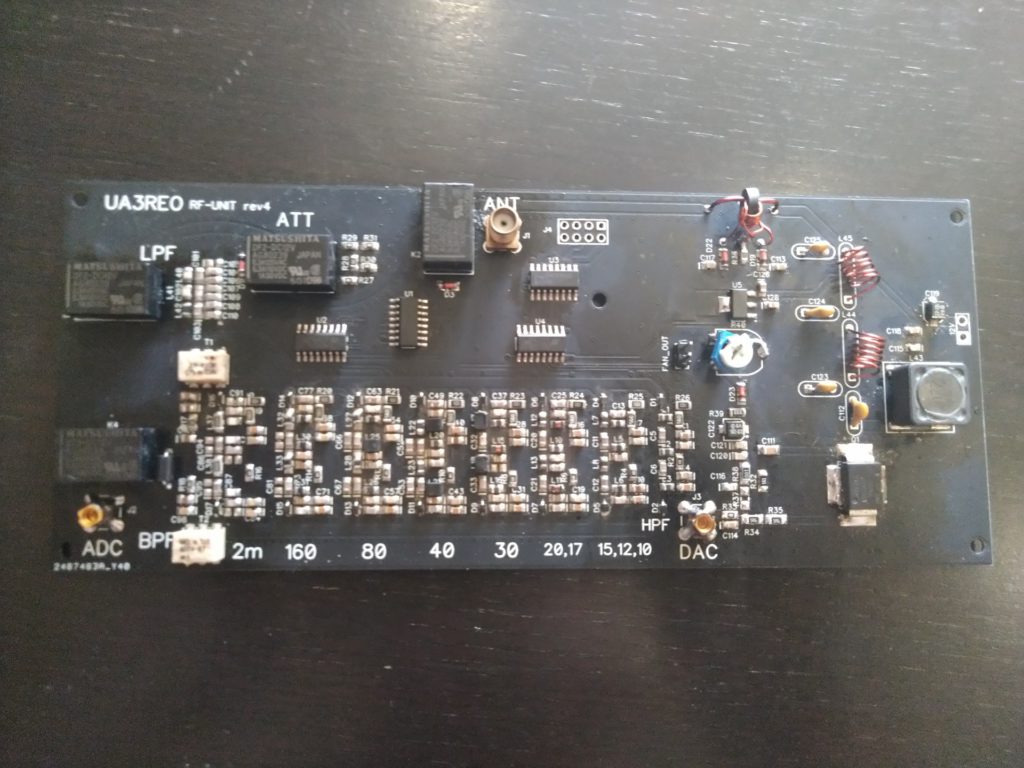

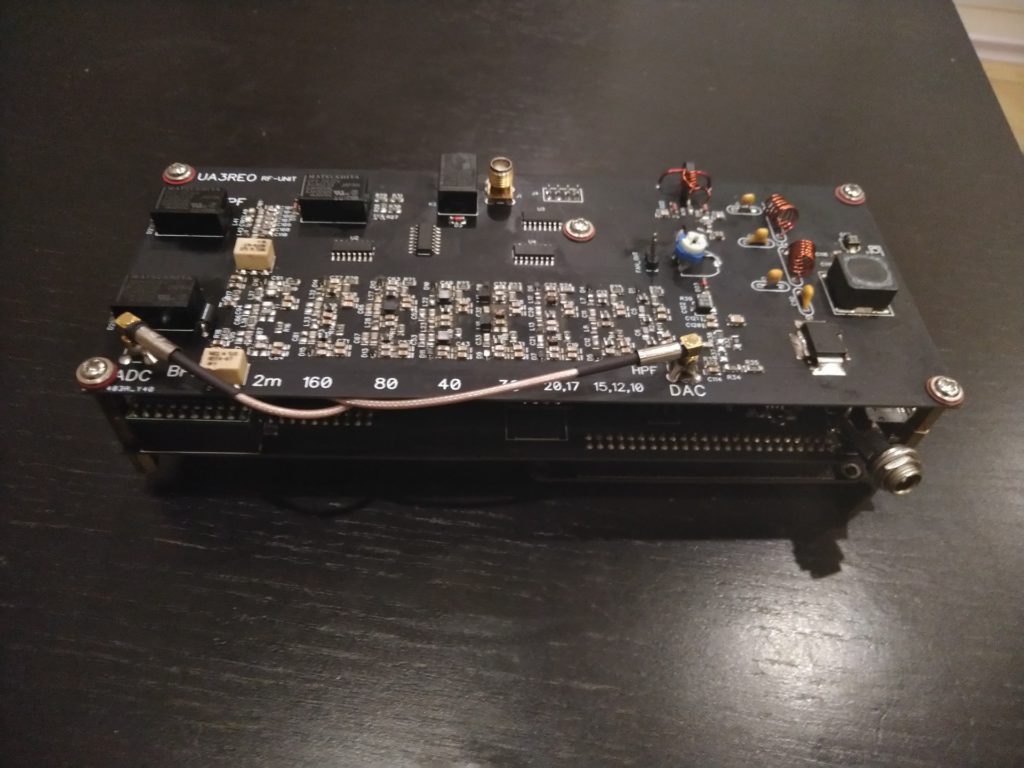

+HARDW: Обновлена плата RF-UNIT, теперь она совмещена с усилителем на ST PD55008-E

+HARDW: Добавлены управляющие выводы на вентилятор

+HARDW: Добавлен КСВ-метр

Обновлена плата ВЧ узлов, усилитель явно не вышел и будет переделан, эту часть платы к повторению не рекомендую.

+STM32: В settings.h добавлена возможность переворота экрана

+STM32: Оптимизация DSP кода и шины обмена | Thx to RA4ASN

+STM32: Управление вентилятором во время и после передачи

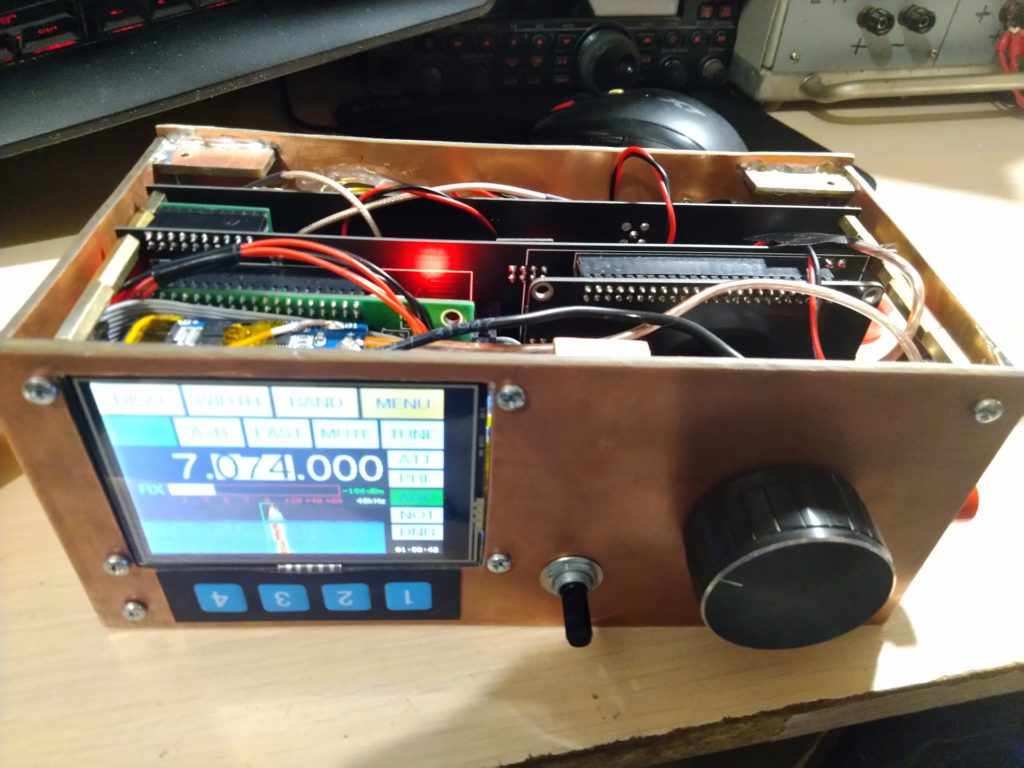

+STM32: Добавлена поддержка клавиатуры и вторичного энкодера на передней панели

Файлы проекта доступны в 2х версиях (в архиве на момент публикации, и в репозитории github, постоянно обновляемые и с исправлениями ошибок), в них включены файлы и исходные коды прошивок, даташиты, схемы и чертежи плат.

Архив проекта версии 1.7

Репозиторий проекта на GitHub

Архив статей по проекту

Можно схемы в виде фоторисунка предоставить, то я не могу их посмотреть

Ааа, так это не тачскрин глючит, а предусилитель теперь сам включается ))) Я уж думал было — все, финиш, тач накрылся, сам кнопки нажимает )))

Кстати… Попробуйте PD55003-E — у него в отличии от PD55008-E можно подобрать режим с выходным сопротивлением под 50 ом.

Модуль SPI в ПЛИС, который для флеш-памяти, пригоден для реализации обмена данными с контроллером?

Думаю вполне, например в трансивере Аист обмен как раз идёт по SPI, можно сделать по аналогии.

Решил скомпилировать Аист на 746g, а фигвам — ld.exe: tc1_stm32f746zg_rom.elf section `.heap’ will not fit in region `RAM’, ld.exe: region `RAM’ overflowed by 25432 bytes.

А какой проект?

Тут тяжело диалог вести. В скайп по позывному или вотсап телеграмм.

Hello! UA3REO RF Transformer can use Mini TC4-1T 1:4 Transformer

Hello! Yes, it will be even better and more compact

Будет продолжение работы над трансивером? Собирать можно? Может есть где видео работы.

Добрый день! продолжение будет, сейчас обновляю аппаратную часть трансивера, перехожу на 16ти битный АЦП, новые платы, а ещё предстоит переписать кучу кода.

Насчёт собирать — смотря с какой целью, если для повышения навыков программирования и конструирования — да, это неплохая база для экспериментов.

Если же рассматривать трансивер для «повседневки», без желания копаться и дорабатывать — нет, ещё очень рано, я постоянно меняю что-то в схеме, дорабатываю, много функций в коде ещё сырые и требуют доработки.

Видео старых версий есть в этой ветке форума, а с новых видео пока не записывали. http://www.cqham.ru/forum/showthread.php?38419-DDC-SDR-%EF%F0%E8%B8%EC%ED%E8%EA-%E8-DDC-DUC-%F2%F0%E0%ED%F1%E8%E2%E5%F0-%EE%F2-UA3REO&p=1634742&viewfull=1#post1634742

Планируете ли вы расширить диапазон частот приемопередатчика до 10 м в следующей версии?

Да, обязательно будет.

Добрый день, Дмитрий!

В версии 1.7 возможна ли полноценная замена EP4CE22

на EP4CE15. Совпадают при этом их выводы?

Здравствуйте, Дмитрий.

Можно ли в версии 1.7 полноценно заменить EP4CE22 на EP4CE15.

Совпадает ли у них цоколёвка?

Приветствую!

Прошивка 1.7 точно поместится, она занимает 12943 блока, а в EP4CE15 имеется 15408. Цокалёвка должна совпасть, т.к. в EP4CE22 просто заменили часть IO выводов на дополнительные входы питания для ядра и PLL. Но я не проверял, на 100% утверждать не могу, только предполагаю.

Для версии 1.8 и выше уже EP4CE15 не подойдёт, т.к. там будут 16ти битный АЦП и прочие доработки.

Трансформаторы для сего девайса дорогие, заразы.

Берем колечки 7х4х2 1000(так заявили в магазине)

— для 1:1 мотаем в 4 провода (у меня 0,12 мм) 6 витков, конец первой обмотки соединяем с началом второй, в итоге получится первая обмотка со средней точкой. Конец третьей с началом четвёртой, получится вторая обмотка со средней точкой. Длинна выводов минимальна. На одну паяем резюк 50 Ом. Подключаем к антенному анализатору и смотрим. Если завал сверху — уменьшаем витки, перематываем на 5. Если завал снизу — перематываем на 7 витков.

— для 1:4 мотаем в 3 провода. Первая и будет первой, конец второй соединяем с началом третьей и получаем вторую обмотку. Дальше по аналогии, только резюк 200 Ом.

За час можно легко сделать.

Уважаемый Дмитрий, судя по проведённой работе релиз 1.7 трансивера является вполне законченным устройством, доступным для повторения многими начинающими в области DUC-DDC. Его привлекательность, в том числе — в недорогих компонентах. К тому же, новые версии Вами задуманы на другой элементной базе. Однако использование отдельных модулей (отладочных плат ПЛИС и МК), в общем случае, не является оптимальным вариантом построения схемы трансивера. В частности, мне бы хотелось иметь схему ( наверное и не только мне) с применением микросхем, в первую очередь, ПЛИС и МК не в формате отладочных плат.

Не сочтите за большой труд, сообщите точный список, что можно исключить из схем отлад. плат.

Не нашёл в вашем архиве схемы платы ПЛИС.

Вячеслав, приветствую!

В версии 1.8, релиз которой будет уже на днях (доделываю последние косметические изменения и исправления багов) произведён полный отказ от готовых модулей FPGA/STM, схемы и платы также будут в архиве проекта, вместе с полным списком изменений.

Спасибо за интерес к проекту!

Вячеслав я поддерживаю ваше желание . Можно остановится на определенном этапе проекта . Нарисовать платы и собрать трансивер. Я думаю что будут желающие на такой вариант .Ну а автор будет совершенствовать дальше трансивер . Потому что остановится трудно и хочется сделать лучше и лучше.