Небольшая инструкция по прошивке FPGA.

Вариантов прошивок несколько, я использую 2:

-Временная прошивка через SOF файл. Прошивает текущую конфигурацию FPGA, но не сохраняет её в flash-память. Позволяет быстро и оперативно протестировать изменения, а в случае ошибки, FGPA возвращается в исходное состояние простой перезагрузкой устройства.

-Постоянная прошивка через JIC-файл, она прошивает flash-память, подключенную по SPI к FPGA в режиме Active Serial. Такой вид прошивки медленный, требует перезагрузки FPGA, и используется только для заливки итоговых прошивок. Сам JIC файл формируется из SOF файла.

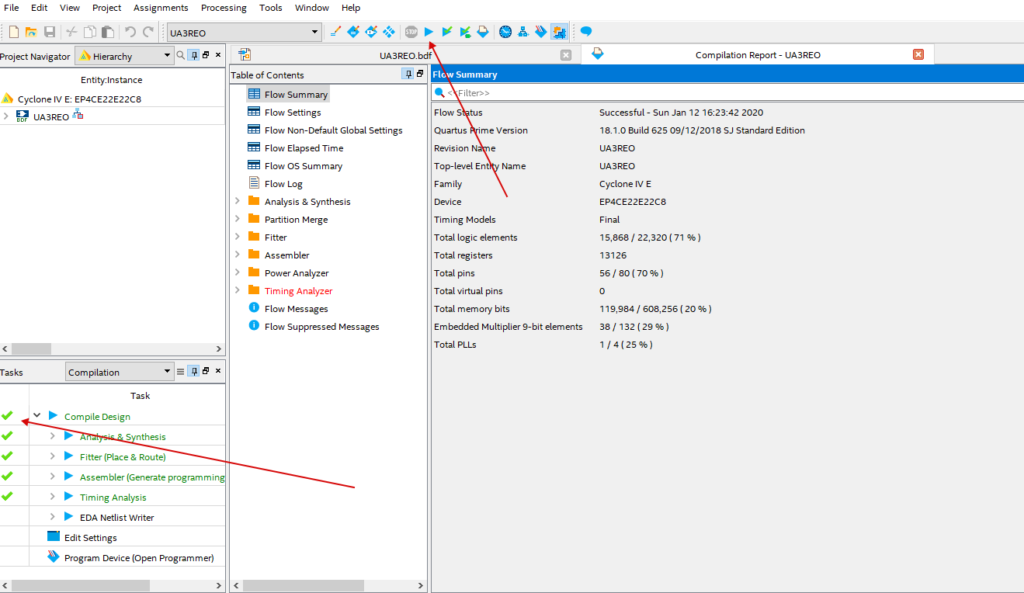

Итак, первым делом компилируем наш проект после необходимых изменений.

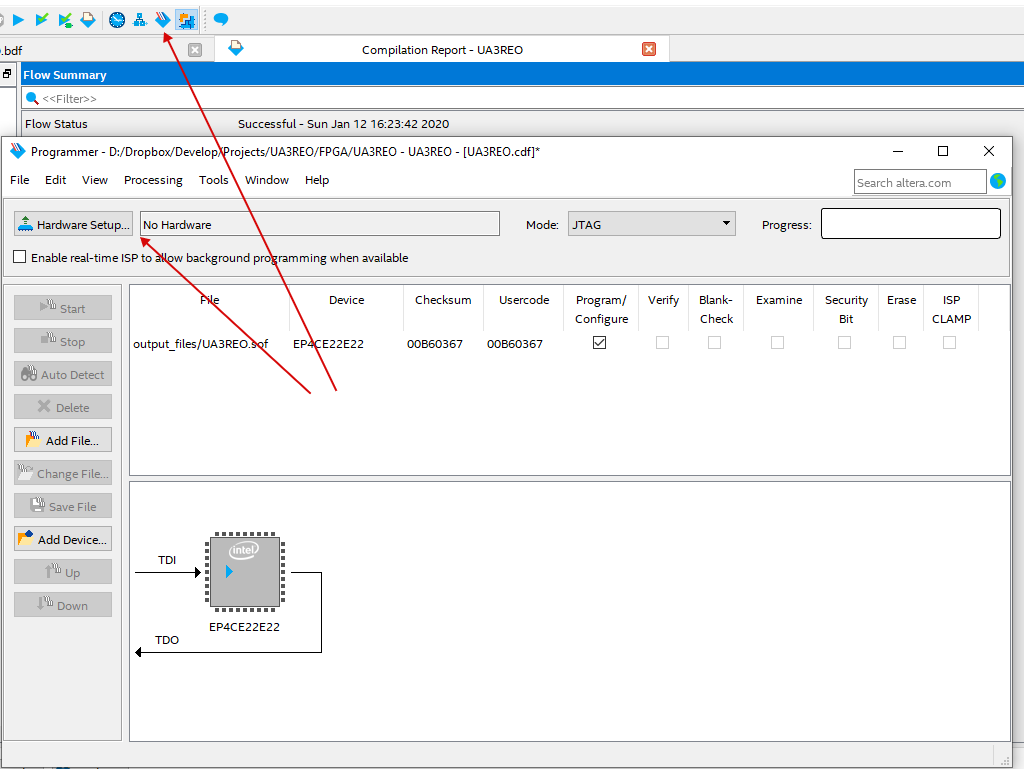

Далее проверяем полученный SOF файл временной прошивки, открываем программатор и проверяем что кабель USB-Blaster найден.

Если не найден (как на скриншоте), заходим в параметры Hardware Setup и выбираем устройство. Если его вообще нет — надо проверить драйвера.

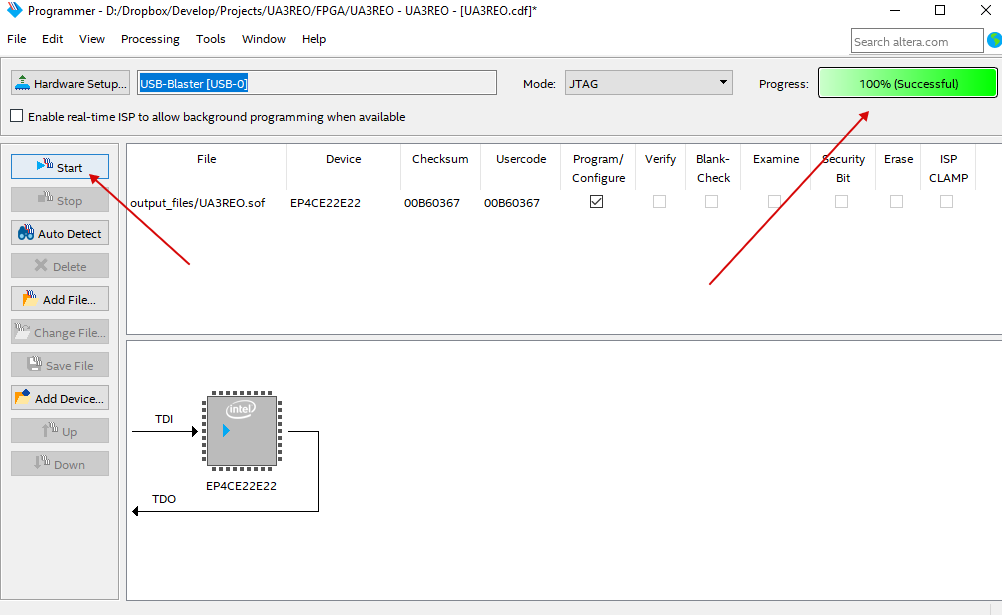

Запускаем процесс прошивки, и по его окончанию новая прошивка сразу должна заработать на устройстве.

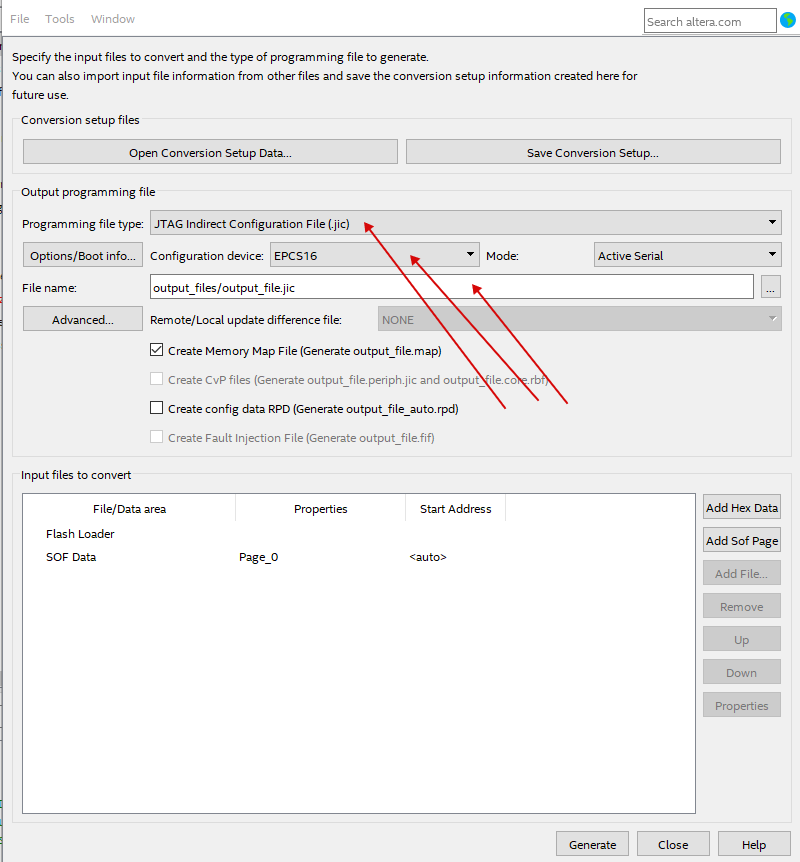

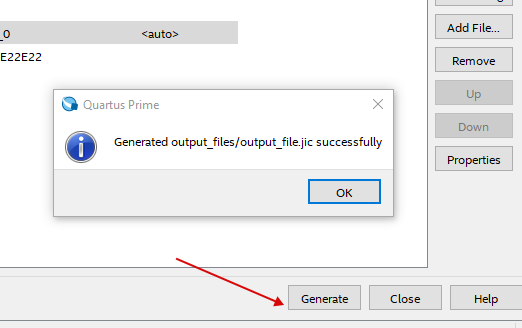

После отладки временной прошивки необходимо сформировать постоянную, на JIC файле, для этого открываем меню конвертации.

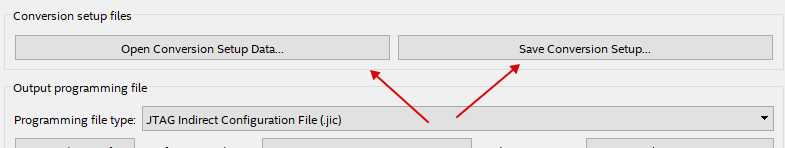

Выбираем формат файла, тип используемой flash-памяти и файл для вывода результата.

Отключаем проверку ID (не обязательно, но без этого, порой, прошивка не работает).

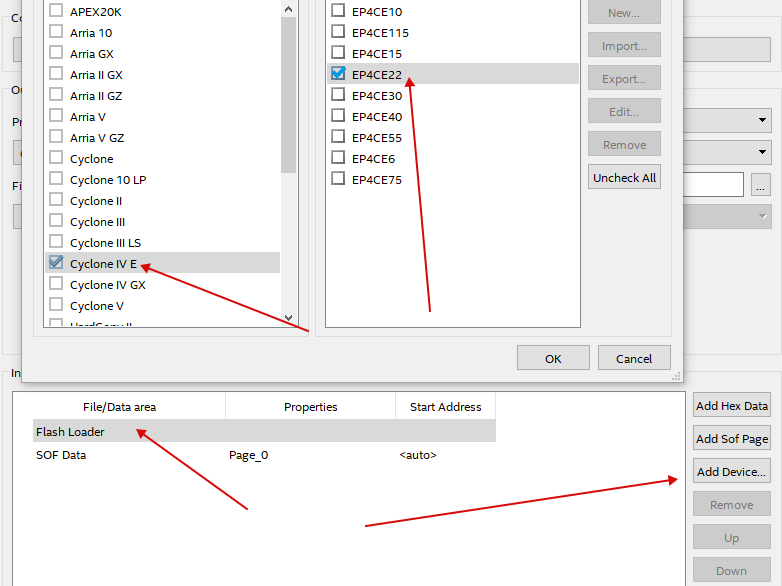

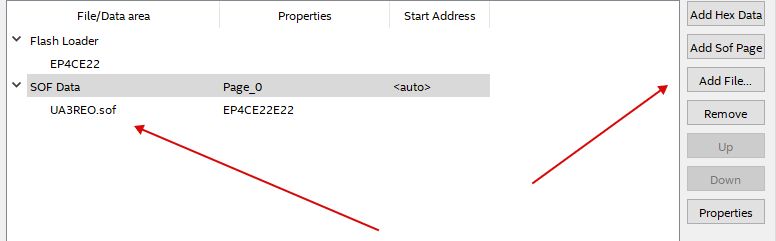

Выбираем используемую модель FPGA.

И добавляем используемый ранее SOF файл.

Запускаем генерацию JIC файла.

Чтобы каждый раз не делать эти настройки, можно сохранить профиль и потом загружать готовый.

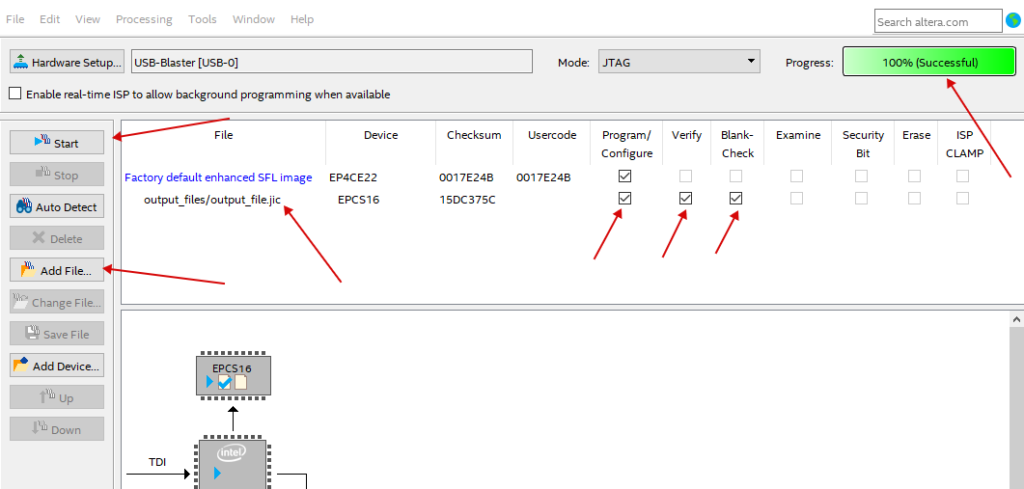

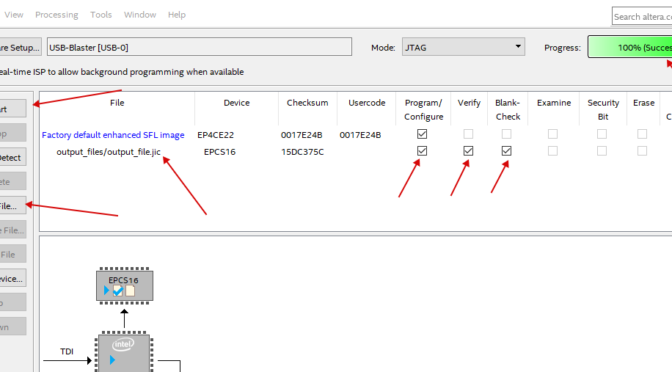

Теперь приступаем к прошивке, но выбрав уже JIC файл и проставив все чек-боксы.

Теперь необходимо перезагрузить FPGA, готово.

Спасибо!!! Очень доходчиво и подробно!!!

А нет ли возможности в квартусе добавить на панель кнопку с этой конвертацией?

Не находил, но можно автоматизировать процесс конвертации, запуская его после компиляции автоматом, статья https://www.intel.com/content/www/us/en/programmable/support/support-resources/knowledge-base/solutions/rd10312014_481.html

Привет UA3REO,

Поздравляю с очень интересным проектом, и я хотел бы поблагодарить вас за это.

Платы для версии 1.8 почти готовы, поэтому сегодня я попытался скомпилировать прошивку FPGA в соответствии с вашими инструкциями. К сожалению, Quartus 18.1 (протестированные как стандартные, так и облегченные выпуски) не создаст файл .SOF.

Ошибка: Can’t generate programming files for your current project because you do not have a valid license for the following IP core or cores. (ID: 115003)

В Quartus я не вносил никаких изменений в настройки компиляции или IP-компоненты, я точно следовал инструкциям. Файл был создан, только если я включил режим оценки IP FPGA в настройках компиляции. (* _time_limited.sof файл создан)

Любая идея, как это исправить или мне нужно купить полную версию Quartus или некоторые библиотеки? Или не могли бы вы выслать мне скомпилированную версию прошивки FPGA 1.8.2? (и в идеале HEX для STM32F407, потому что эта компиляция еще впереди 🙁

Радек

Чехия

Немного фотографий: https://photos.app.goo.gl/RNKn1HpgNZsBR3Be9

Приветствую! Спасибо за интерес к проекту. Всё верно, не хватает лицензионного ключа для компиляции.

Я Вышлю Вам на почту файлы проекта.

Спасибо! Все очень доходчиво!

Дмитрий, а подскажите, пожалуйста: что за шнурок USB-Blaster вы используете для прошивки Циклона?

Для СТМ-а, так понимаю, хватит китайского ST-Link mini?

Спасибо!

Для циклона китайский бластер, вот типа такого https://aliexpress.ru/item/4001359125879.html

Для STM32 да, обычный мини, под него как раз распиновка на плате и сделана.

Tnx!

Не дёшево, однако 🙂

Нашёл, что китайцы клепают такие программаторы двух типов (по элементной базе): на PIC или STM контроллерах. У второго типа бывают проблемы с драйвером на Win10 — приходится искать другой драйвер. У вас нормально работает прогер? Не смотрели, на чём собран?..

У меня тоже китай — драйвера стоят от Quartus 13ой версии, работают вполне себе неплохо. Если брать драйвера чуть свежее — уже не заводится.

OK, спасибо!

Hello great project, but i also dont get the files right, can you send me also the files?

And for the STM32 the .hex file, or will that be made?

I am almost ready to flash the 2

Greetings

Rolf

Please visit our telegram channel. I can not post a link for licensing reasons.