На стыке интересных мне областей программирования и радио зародился долгий, но интересный проект по созданию цифрового приёмника прямого преобразования, в котором аналоговых частей будет абсолютный минимум.

С каждой частью статьи я планирую дорабатывать приёмник, улучшать его характеристики, обвешивать его разными доработками, а в итоге возможно и получить полноценный трансивер.

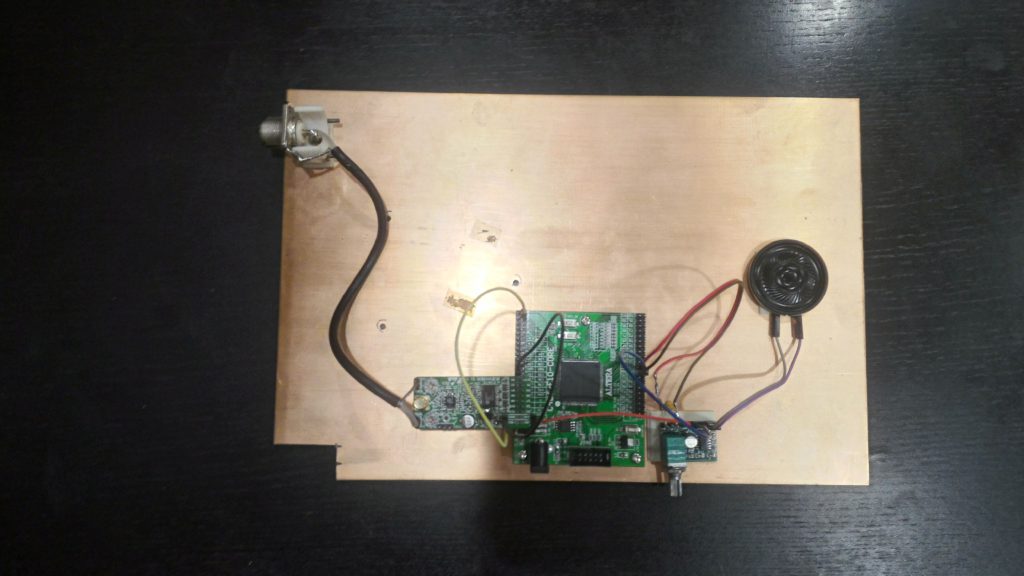

Базовый комплект будет построен на китайской АЦП AD9226.

Цифровым сердцем приёмника будет являться FPGA матрица Altera EP4CE10.

Для того, чтобы не мучатся с наушниками добавлен простейший УНЧ с питанием в 5 вольт и динамик.

Итак, соединяем все воедино (точки подключения особой роли не играют, всё настраивается и назначается программно).

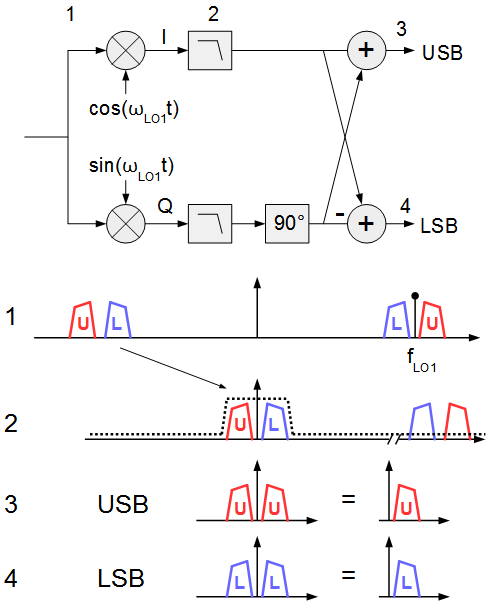

Идея приёмника заключается в смешивании оцифрованного с помощью АЦП радиосигнала с гетеродином, выдающим 2 сигнала со смещением в 90 градусов (синус и косинус).

Тем самым мы получаем комплексный сигнал (I и Q), с помощью которого достаточно легко добиться подавления зеркального канала и демодулировать полезный сигнал.

Устанавливаем среду разработки Quartus.

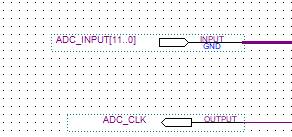

Начинаем с подключения АЦП (вход и тактовый сигнал). Т.к. внешнего кварцевого генератора нет, будем тактовать модуль силами самой FPGA (а это очень плохо в плане качества приёма, но для первой версии сгодится).

Добавляем вход кварцевого генератора планы FPGA (50 мегагерц).

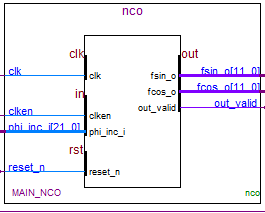

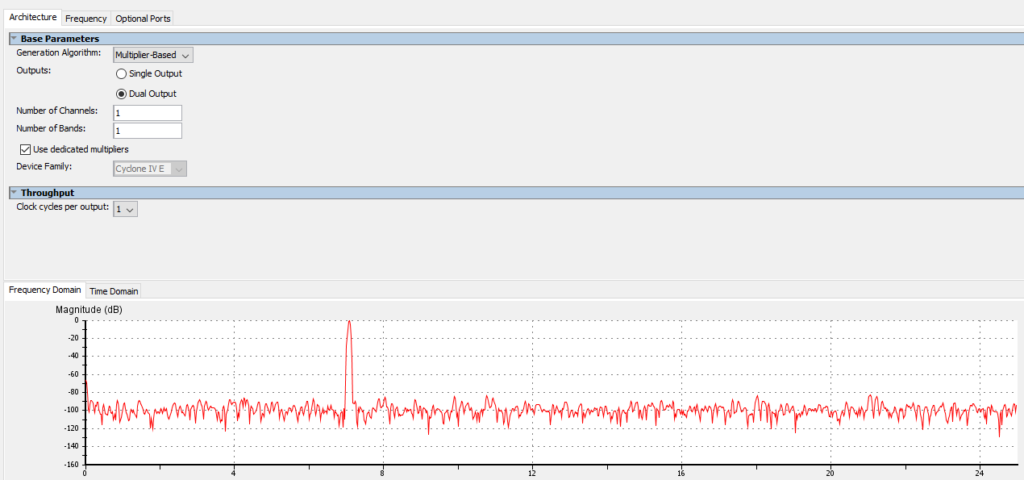

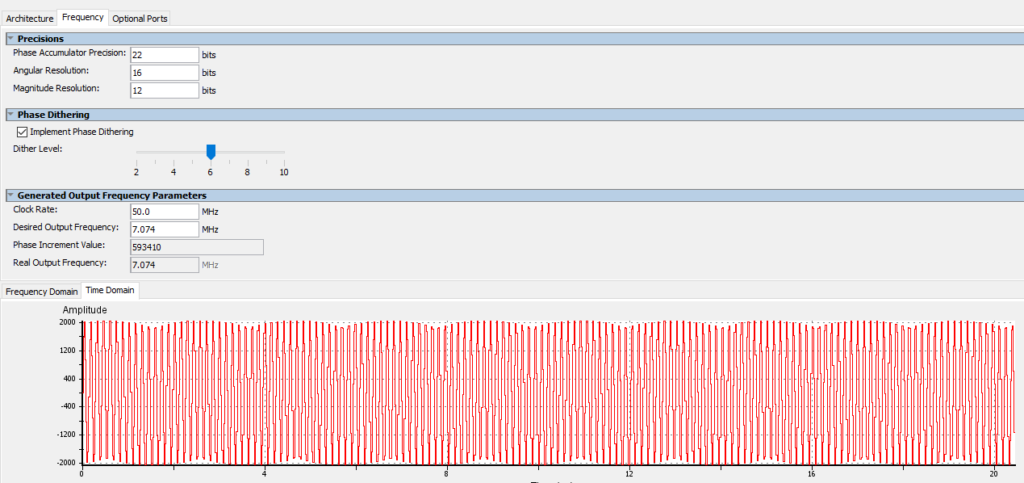

Первым делом создаём гетеродин, настроенный на частоту приёма. Его задача состоит в переносе частот с диапазона радиоволн в звуковой.

Его параметры на скриншотах:

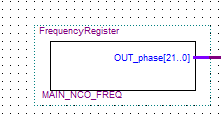

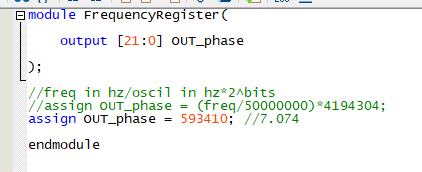

Для управления частотой гетеродина в него необходимо передать слово частоты, задающее смещение фазы, для этого подготовим отдельный модуль. Сейчас частота будет статична, но дальше планирую менять её энкодером.

Слово частоты это число, получаемое делением необходимой частоты в герцах на частоту кварцевого генератора и умноженную на двойку в степени, равной разрядности DDS-генератора (гетеродина).

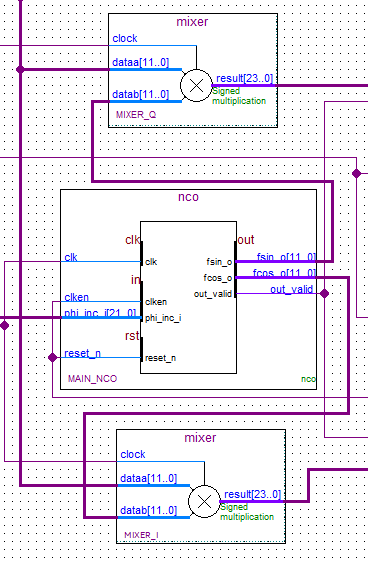

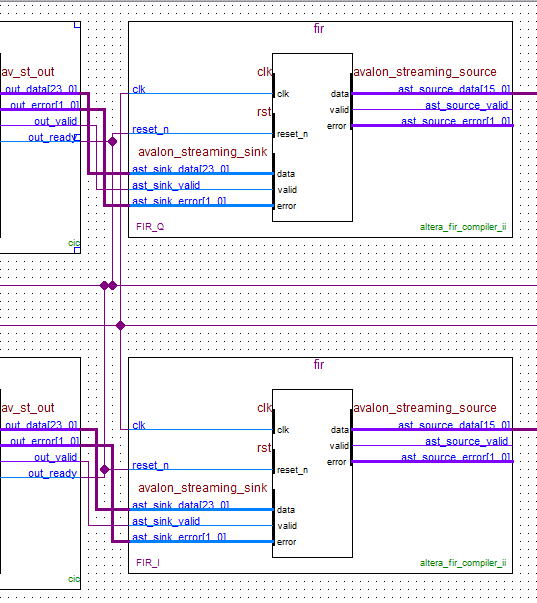

Полученный сигнал подаём на 2 смесителя (умножителя), которые обеспечивают смешивание сигнала АЦП (вход А) с сигналом гетеродина (вход B).

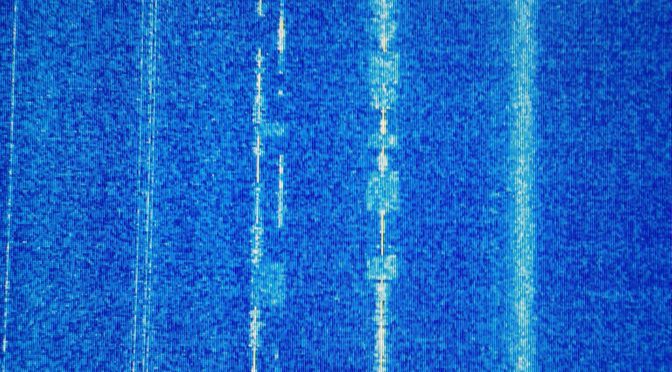

Полученный сигнал смещён на частоту гетеродина, т.е. выбранная частота теперь размещается в нулевой. А слева (да, в отрицательной части) и справа от неё находятся весь необходимый нам спектр.

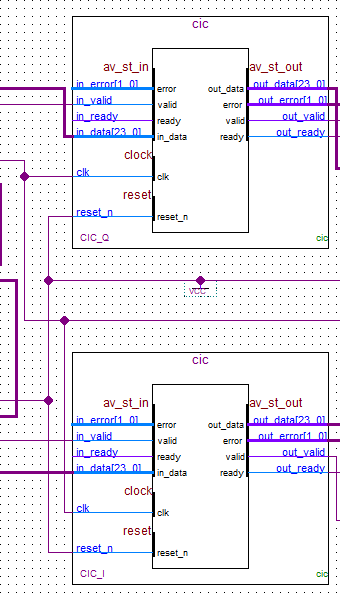

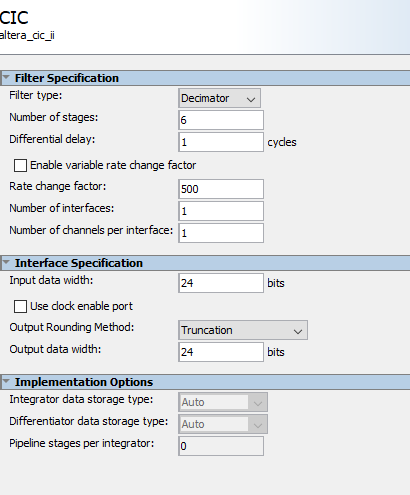

Чтобы дальше эффективно работать с сигналом, нам необходимо его децимировать (уменьшить частоту выборок), эту роль выполняет CIC фильтр.

После этого частота выборок сокращается с 50 миллионов раз в секунду до 100 000.

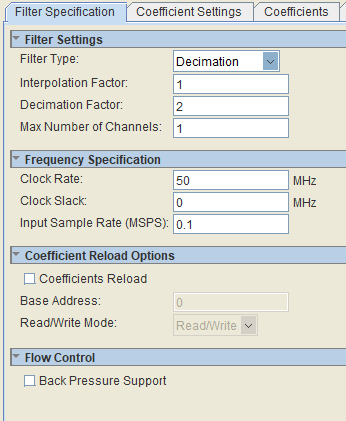

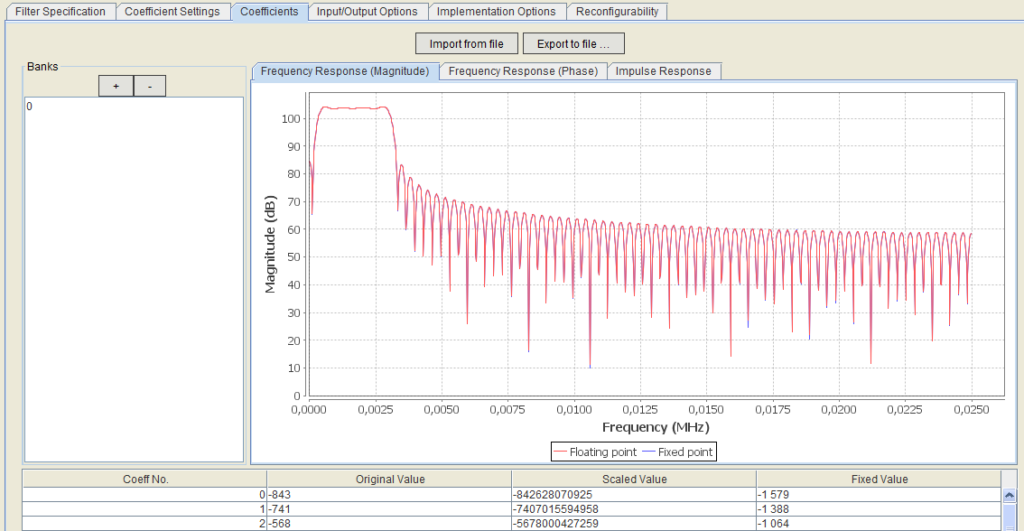

Далее нам необходимо сделать полосовой фильтр, т.к. будем принимать SSB сигнал, то фильтр полоса пропускания потребуется в районе 2700гц. Для этого воспользуемся фильтром конечных импульсных характеристик (FIR).

Для его расчёта удобно использовать следующие программы:

Iowa Hills FIR Filter Designer

WinFilter

Также, фильтр сократит число выборок с 100 000 до 50 000, что подходит для вывода на динамик.

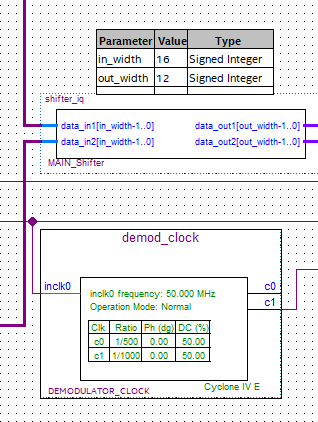

Далее сокращаем разрядность (количество бит) в потоке для дальнейшей обработки.

Ещё, потребуется PLL модуль для тактования частоты 50кгц (равной частоте дискретизации потока на текущем этапе).

Полученные сигналы уже можно выводить на динамик, но мы не избавились от основной проблемы приёмников прямого преобразования — зеркального канала. Т.е. слушая передачи слева и справа от принимаемой частоты будем принимать их одинаково хорошо. Необходимо получить однополосный приём.

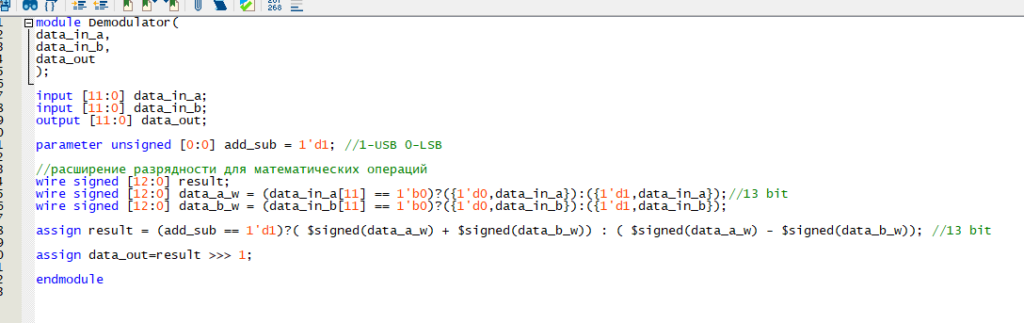

Для этого поток Q (смешанный с синусом) необходимо довернуть по фазе на 90 градусов, тем самым потоки I и Q будут относительно друг друга в 180 градусах. Их дальнейшее сложение или вычитание будет давать USB и LSB полосу приёма соответственно, подавляя всё лишнее.

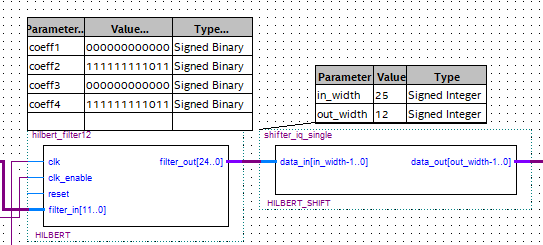

Помочь нам в этом может преобразователь (фильтр) Гильберта, рассчитанный в программе MatLab.

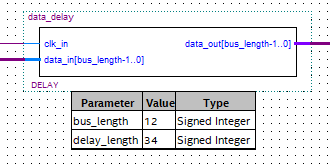

Т.к. фильтр Гильберта вызывает задержку сигнала на ((количество ступеней фильтра-1)/2) то необходимо задержать сигнал I на столько же шагов.

Далее мы можем сложить (или вычесть) коплексные составляющие сигнала, получив необходимую полосу приёма.

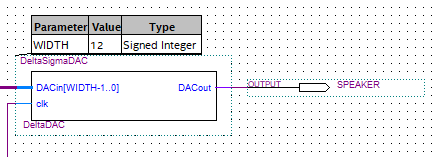

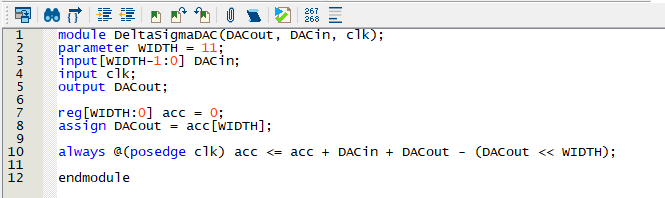

Итоговый результат подадим на дельта-сигма модулятор, смысл работы которого заключается в восстановлении синусоидального сигнала из ШИМ с помощью RC-цепочки (резистор 3.3к, конденсатор 47нф).

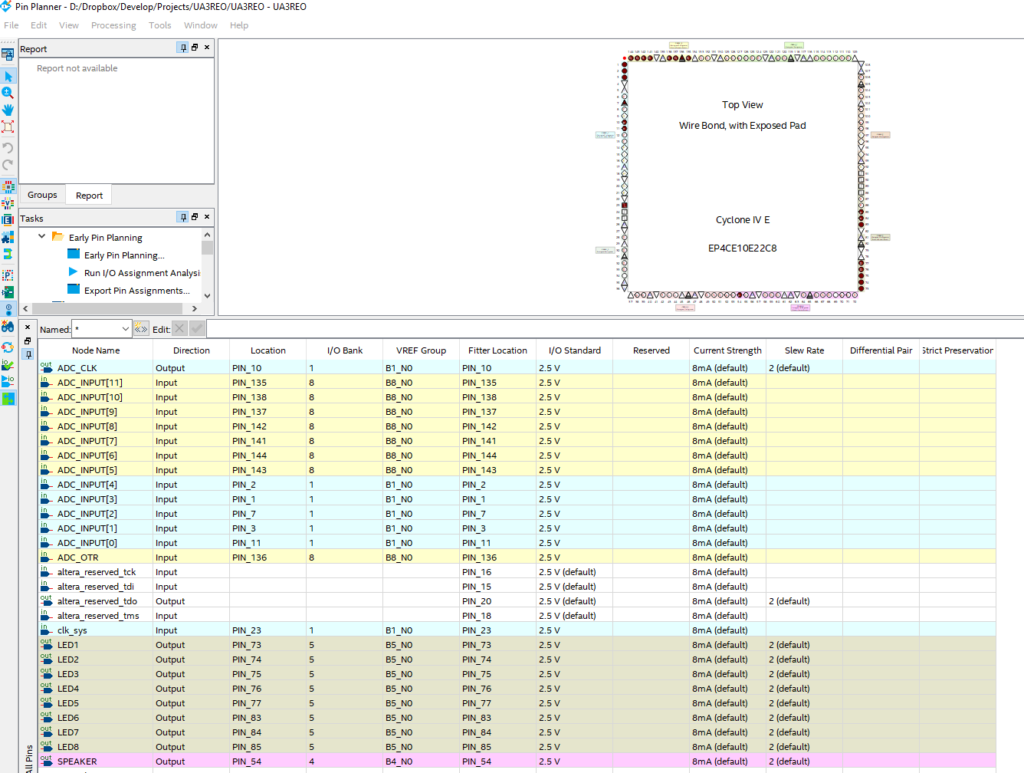

Программный код готов, можно привязать выводы в прошивке к ножкам FPGA.

Готово, можно включить приёмник, подключить антенну ко входу АЦП и наслаждаться его работой.

Следующим шагом наверное буду делать УВЧ, управление частотой, дисплей.

Исходники прошивки тут.

При создании были использованы материалы следующих статей, без которых было бы не реально сделать хоть что-то, огромное спасибо авторам.

- http://we.easyelectronics.ru/Radio/prostoy-cifrovoy-radiopriemnik.html

- http://we.easyelectronics.ru/Radio/prostoy-cifrovoy-radiopriemnik-chast-2.html

- http://we.easyelectronics.ru/Radio/prostoy-cifrovoy-radiopriemnik-chast-3.html

- https://habrahabr.ru/post/204310/

- https://geektimes.ru/post/258810/

- http://www.polesite.ru/?p=3260

- https://habrahabr.ru/post/274847/

- http://r4n.su/?page_id=777

- http://www.panoradio-sdr.de/ssb-demodulation/

- http://www.radiostation.ru/drm/phasefilter.html

- http://www.ece.ucsb.edu/Faculty/rodwell/Classes/ece218b/notes/quad_mixing.pdf

Здравствуйте Дмитрий. Вопрос по коэффициентам FIR-фильтра. Я загружаю в визард коэффициенты одного фильтра но в разном формате: Fixedpoint и Float и получаются разные АЧХ. На форуме Марсохода: https://marsohod.org/forum/5-altera-quartus-ii/1256-voprosy-novichka?start=230#7728 , мне ответили что это масштаб другой. Посмотрите пожалуйста там прикреплены две картинки по таблице видно что данные одни. Получается не важно, какие значения на оси Y, главное относительные величины пропускаемого диапазона частот и подавляемого? В этой статье тоже полезный сигнал «усиливается на сто db», чему верить?

Принципиального различия в формате чисел я не увидел, одно время даже написал конвертер из float в integer https://ua3reo.ru/services/float_to_dec_coeff.php

Дмитрий,

Наконец то нашел автора, который доходчиво объясняет подход к программированию на ПЛИС. Если знаешь структуру ППП, то разобраться в графической среде программирования не сложно, особенно, когда мысли излагаются так доходчиво. Есть один вопрос, не совсем в тему- я хочу собрать приемник с полным управлением и демодуляциеё на компе,и потому мне блоки демодуляции не нужны-их можно организовать программно, например в HDSDR , но вот как организовать управление и передачу на комп I Q потоков например через LAN8720 Модуль. Если бы вы такой проект в блоге написали было бы великолепно, а если нет-то хотя бы носом ткните в подобный проект с графическим отображением такого СДР приемника. А то что-то я подвис…Заранее спасибо!

Добрый день, спасибо!

Такой проект уже есть, активно собирается и обсуждается, код открытый, вот ссылки:

http://www.cqham.ru/forum/showthread.php?35923-DDC-DUC-%F2%F0%E0%ED%F1%E8%E2%E5%F0-%F1-%E8%ED%F2%E5%F0%F4%E5%E9%F1%EE%EC-Ethernet-%E8%E7-%EC%EE%E4%F3%EB%E5%E9-%F1-%C0%EB%E8

http://www.cqham.ru/forum/showthread.php?37592-%C1%FE%E4%E6%E5%F2%ED%FB%E9-%E4%E2%F3%F5%EA%E0%ED%E0%EB%FC%ED%FB%E9-%EC%EE%E4%F3%EB%FC%ED%FB%E9-DDC-DUC-%CA%C2-%D3%CA%C2-%CF%D7

Дмитрий,

Спасибо за ответ, но проект там без графических файлов, Даже в самой первой теме про приемник, структура ресивера не раскрыта, и не понятно как там все связано в этом кодрике…а для меня код в виде текстов — темный лес. Последний раз я занимался этим в институте 30 лет назад на бейсике )) , и пытаться заниматься этим на языке VHDL пока непосильная ноша. А просто прошить и пользоваться я не люблю. Может что другое посоветуете проект или популярно написанную статью?

73!

Пока вроде не встречал такого… даже не знаю что посоветовать ещё

Хорошо. Спасибо. …

У вас много полезного про проектирование фильтров в квартусе узнал. Осталось прилепить блок ethernet. Будем копать дальше.

Дмитрий, простите, что беспокою. Вывод OTR от АЦП обязательно использовать в компьютерном варианте? Или это только для индикации уровня переполнения микросхемы?

Добрый день!

Это только индикатор перегрузки по входу, использовать не обязательно, но с ним удобнее.

спасибо!

Дмитрий, приветствую! Указанную Вами плату FPGA не нашел, а такая пойдет https://aliexpress.ru/item/1005001382793644.html?spm=a2g0o.productlist.0.0.1a204275IKUIOC&algo_pvid=d1574638-ad66-41fd-961b-c17c3013a78d&algo_expid=d1574638-ad66-41fd-961b-c17c3013a78d-8&btsid=0b8b15cb16034707510395930ee8f9&ws_ab_test=searchweb0_0,searchweb201602_,searchweb201603_

если да, то что то менять или переделывать надо?

Спасибо! С уважением Дмитрий. UT4NJ 73!

Дмитрий, здравствуйте! конечно подойдёт, отличие только в корпусе FPGA, из изменений — только указать необходимые пины, которые удобно использовать на этой макетной плате, дальше должно всё заработать на отлично.

Большое спасибо Дмитрий! Много собрал трансиверов за свою жизнь, но с этой техникой приходится почти все начинать сначала.

С большим интересом читаю Ваши статьи, букварь для меня.

Еще раз спасибо, что не смотря на загруженность с Волком, находите время ответить. Здоровья Вам и удачи!

Интересная статья! Пробовал сделать преобразование Гильберта на STM32F303 — при частоте сэмплирования хватало производительности на 8кГц сэмплирования.. да еще звук был с кучей артефактов (как будто заворачивание спектра) не смотря на ФНЧ по входу а также предварительной фильтрации тестового сигнала с ПК — вообщем одно разочарование.

Насчет ПЛИС — не смог тянуть: ибо это хуже тяжелее ассемблера! .Лет 5 назад попробовал программировать Altera — были разные простые задачи типа сумматора на VERILOG и вывода на светодиоды.Потом в конце написал последовательный порт для подключения i2C АЦП и ЦАП а также ФНЧ… и целую ночь не мог заснуть от переутомления. После этого осознал что ассемблер это язык высокого уровня по сравнению с VERILOG и благополучно оставил это дело — плату продал через интернет.